Andes Technology has just announced the AndesAIRE product line, where AndesAIRE stands for Andes AI Runs Everywhere, comprised of the AndesAIRE AnDLA I350 (Andes Deep Learning Accelerator) AI/ML hardware accelerator intellectual property (IP) and the AndesAIRE NN SDK with neural network software tools and runtimes.

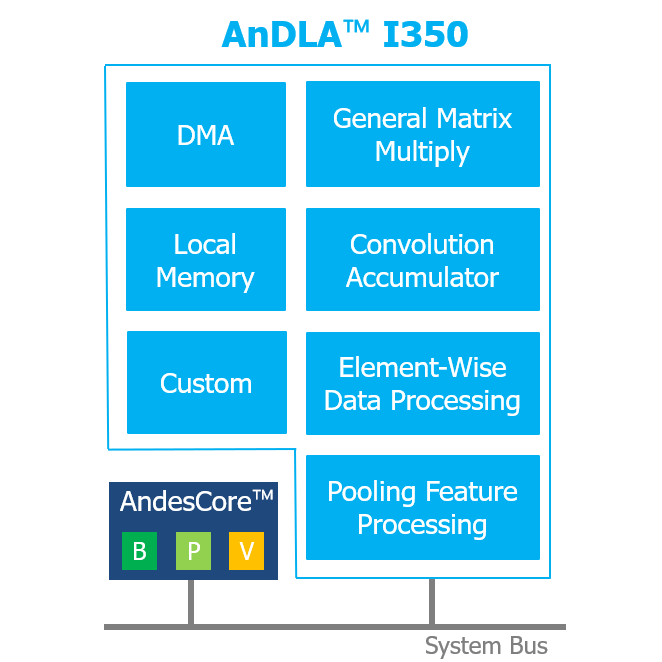

AndesAIRE AnDLA I350

AnDLA I350 specifications:

- Configurable MACs from 32 to 4096 (INT8)

- Maximum performance – 8 TOPS at 1GHz

- Configurable local memory – 16KB to 4MB

- Multi-dimension DMA

- Four 64-bit AXI bus interfaces

- NN type – CNN inference

- NN models

- Image and Video: AlexNet, VGG-16/19, MobileNet-v1/v2/v3, ResNet-8/50, Tiny YOLO v1/v2, YOLO v1/v2/v3/v4/v5, SSD MobileNet v1/v2, Inception v2, EfficientNet-lite, MobileFaceNet, BlazeNet

- Speech/Voice and audio: LSTM, RNN, GRU

- Operators: Conv2d, depthwise convolution, pointwise convolution, transpose convolution, dilated convolution, element-wise (add, sub, mul), fully-connected, activation (ReLU, leaky ReLU, sigmoid, Tanh, ReLU6, SiLU), pooling (max, ave), upsample, concatenation, batch normalization, channel padding

- Operator fusion

- NHWC data format

The IP block appears to offer an alternative to Arm Ethos-U55 and Ethos-U65 microNPUs but for a wider range of applications, since the Arm accelerators are only configurable to deliver 64 GOPS up to 1 TOPS of AI inference. It targets low-power, small-area SoCs designed for edge inference applications such as smart IoT devices, smart cameras, Smart Home appliances, and robotics, and should mostly be used in conjunction with AndesCore RISC-V CPUs with Andes Custom Extension (ACE) where the more demanding AI workloads are computed on the AnDLA and the simple computations can be more efficiently offloaded to the RISC-V CPU(s) with DSP/SIMD or Vector extensions.

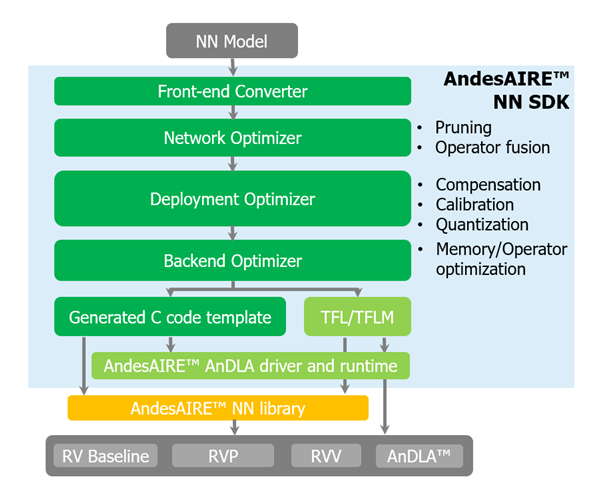

AndesAIRE NN SDK

The AnDLA I350 is supported by the AndesAIRE NN SDK with the following components:

- AndesAIRE NNPilot: a neural network optimization tool suite

- AndesAIRE TFLM for AnDLA: an AnDLA-optimized inference framework running on a host based on TensorFlow Lite for Microcontrollers

- AnDLA driver and runtime

The NNPilot automatically analyzes input NN models, applies model pruning and quantization, and generates AnDLA executables based on its configuration to perform inference together with the TFLM framework, as well as sample host C code to invoke the AnDLA driver in the bare metal environment. Besides TensorFlow Lite, PyTorch and ONNX frameworks are also supported.

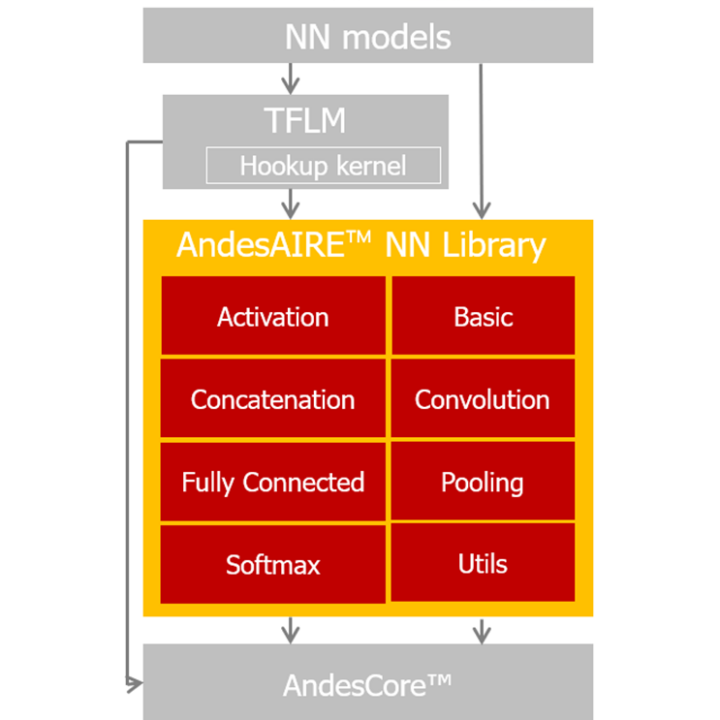

All development is done in the AndeSight IDE, and the company also offers a RISC-V-specific AndesAIRE NN Library with over 170 optimized NN compute functions for RISC-V DSP/SIMD P-Extension (still at the draft stage) and the RISC-V Vector V-Extension v1.0.

Andes Technology says the AndesAIRE AnDLA I350 and the AndesAIRE NN SDK are available for licensing now in an early-adopter program, which probably means we could expect the first RISC-V microcontrollers or application processors with an AnDLA I350 AI accelerator sometimes in 2024. Additional information may be found on the product page and the press release.

Thanks to TLS for the tip.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress