Linux 6.2 has just been released with Linus Torvalds making the announcement on LKML as usual: So here we are, right on (the extended) schedule, with 6.2 out. Nothing unexpected happened last week, with just a random selection of small fixes spread all over, with nothing really standing out. The shortlog is tiny and appended below, you can scroll through it if you’re bored. Wed have a couple of small things that Thorsten was tracking on the regression side, but I wasn’t going to apply any last-minute patches that weren’t actively pushed by maintainers, so they will have to show up for stable. Nothing seemed even remotely worth trying to delay things for. And this obviously means that the 6.3 merge window will open tomorrow, and I already have 30+ pull requests queued up, which I really appreciate. I like how people have started to take the whole “ready for […]

Android 14 developer preview brings enhancements to performance, privacy, security, and user customization

Google has just released the first developer preview of Android 14 with productivity improvements for developers, as well as enhancements to performance, privacy, security, and user customization. Android 14 aims to work better across devices and form factors with improved support for tablets and foldables and adds window size classes, sliding pane layout, Activity embedding, and box with constraints, etc… To help developers, the company also published “Get started with large screens” documentation and released a Cross-device SDK preview. The new version of the mobile operating systems also further streamlines background work to optimize system health and battery life and provide a better end-user experience. This is achieved through updates to JobScheduler and Foreground Services, optimized broadcasts most of which are internal to Android 14, and a new “Exact alarms” permission since it consumes more resources. Android 14 also introduced some user-facing changes with bigger fonts up to 200% with […]

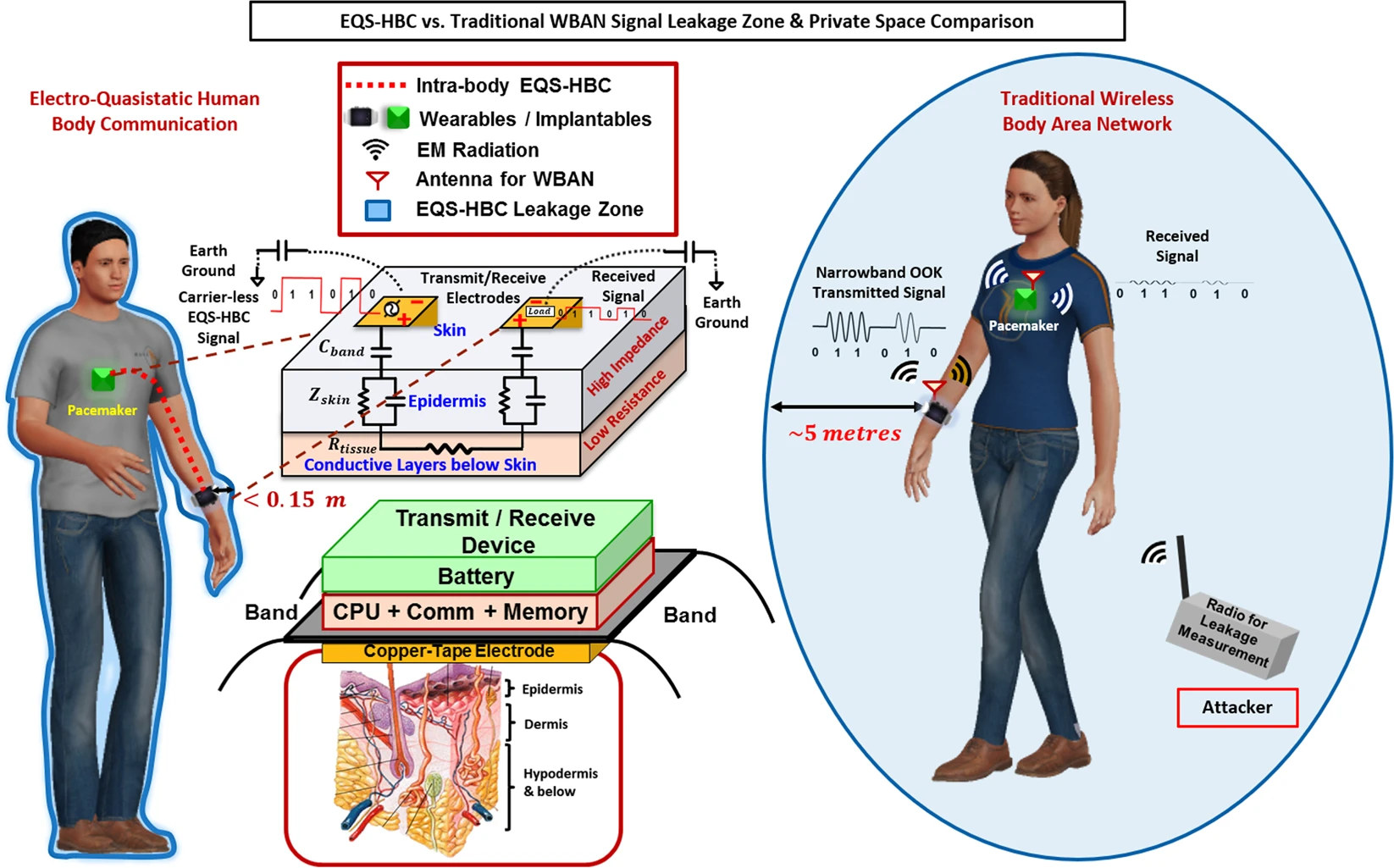

The Wi-R protocol relies on body for data communication, consumes up to 100x less than Bluetooth

The Wi-R protocol is a non-radiative near-field communication technology that uses Electro-Quasistatic (EQS) fields for communication enabling the body to be used as a conductor and that consumes up to 100x less energy per bit compared to Bluetooth. In a sense, Wi-R combines wireless and wired communication. Wi-R itself only has a wireless range of 5 to 10cm, but since it also uses the body to which the Wi-R device is attached, the range on the conductor is up to 5 meters. While traditional wireless solutions like Bluetooth create a 5 to 10-meter field around a person, the Wi-R protocol creates a body area network (BAN) that could be used to connect a smartphone to a pacemaker, smartwatch, and/or headphones with higher security/privacy and longer battery life. One of the first Wi-R chips is Ixana YR11 with up to 1Mbps data rate, and they are working on a YR21 […]

QNAP preps Rockchip RK3588 AI NAS and Intel NAS with hot-swappable E1.S SSDs

QNAP has been teasing two potentially interesting NAS coming up soon: the TS-AI642 AI NAS leveraging the 6 TOPS NPU in Rockchip RK3588 Arm processor for image and facial recognition, and the TBS-574X NAS powered by an Intel Core i3-1220P Alder Lake CPU and taking up to five hot-swappable E1.S NVMe PCIe SSDs. Details are limited since neither device is available yet, but both NAS are equipped with relatively powerful Arm and Intel processors and offer some innovative features. QNAP TBS-574X NAS with Rockchip RK3588 Preliminary specifications: SoC – Rockchip RK3588 octa-core 64-bit Arm processor with 4x Cortex-A76 cores @ 2.2 GHz, 4x Cortex-A55 cores @ 1.8 GHz, 6 TOPS NPU Storage – 6x SATA III bays Video Output – 2x HDMI 2.1 ports Networking – Built-in 2.5GbE, PCIe Gen 3 slot for 10GbE module The main highlight is the 6 TOPS AI accelerator that boosts the performance of the […]

Espressif ESP32-P4 – A 400 MHz general-purpose dual-core RISC-V microcontroller

Espressif ESP32-P4 is a general-purpose dual-core RISC-V microcontroller clocked at up to 400 MHz with AI instructions extension, numerous I/Os, and security features. It also happens to be the first microcontroller from Espressif Systems without wireless connectivity, and as such, it should probably be seen as an alternative to STM32F7/H7 or NXP i.RT Arm Cortex-M7 microcontrollers/crossover processors, and likely offered at a significantly lower cost. It should also offer lower power consumption than other ESP32 chips thanks in part to a third RISC-V core clocked at 40 MHz that can keep the system running while the other two high-performance cores are down. ESP32-P4 key features and specifications: MCU subsystems Dual-core RISC-V HP (High-performance) CPU @ up to 400 MHz with AI instructions extension and single-precision FPU, 768KB of on-chip SRAM Single-RISC-V LP (Low-power) MCU core @ up to 40 MHz with 8KB of zero-wait TCM RAM Memory & Storage I/F […]

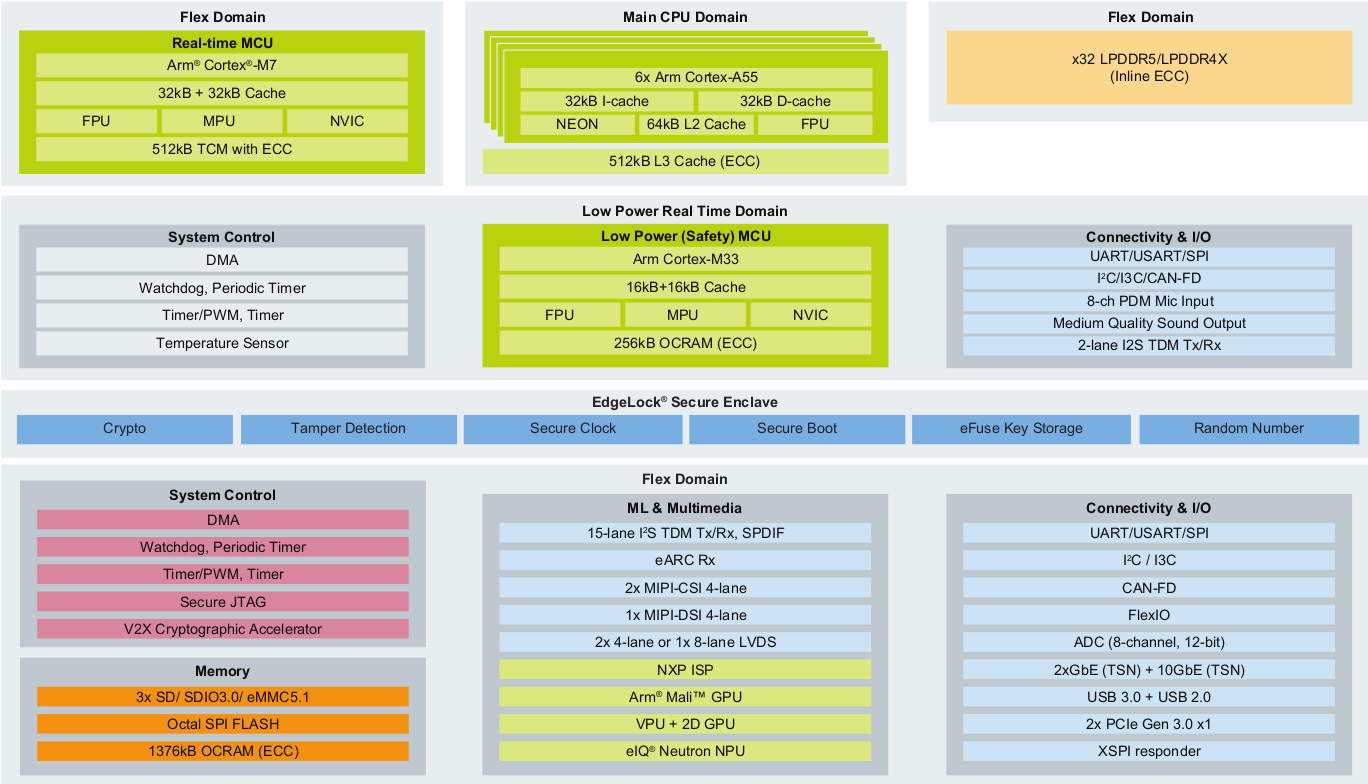

NXP i.MX 95 processor features Cortex-A55, Cortex-M33, and Cortex-M7 cores, eIQ Neutron NPU

NXP i.MX 95 is an upcoming Arm processor family for automotive, industrial, and IoT applications with up to six Cortex-A55 application cores, a Cortex-M33 safety core, a Cortex-M7 real-time core, and NXP eIQ Neutron Neural Network Accelerator (NPU). We’re just only starting to see NXP i.MX 93 modules from companies like iWave Systems and Forlinx, but NXP is already working on its second i.MX 9 processor family with the i.MX 95 application processor family equipped with a higher number of Cortex-A55 cores, an Arm Mali 3D GPU, NXP SafeAssure functional safety, 10GbE, support for TSN, and the company’s eIQ Neutron Neural Processing Unit (NPU) to enable machine learning applications. NXP i.MX 95 specifications: CPU Up to 6x Arm Cortex-A55 cores with 32KB I-cache, 32KB D-cache, 64KB L2 cache, 512KB L3 cache with ECC 1x Arm Corex-M7 real-time core with 32KB I-cache, 32KB D-cache, 512KB TCM with ECC 1x Arm Cortex-M33 […]

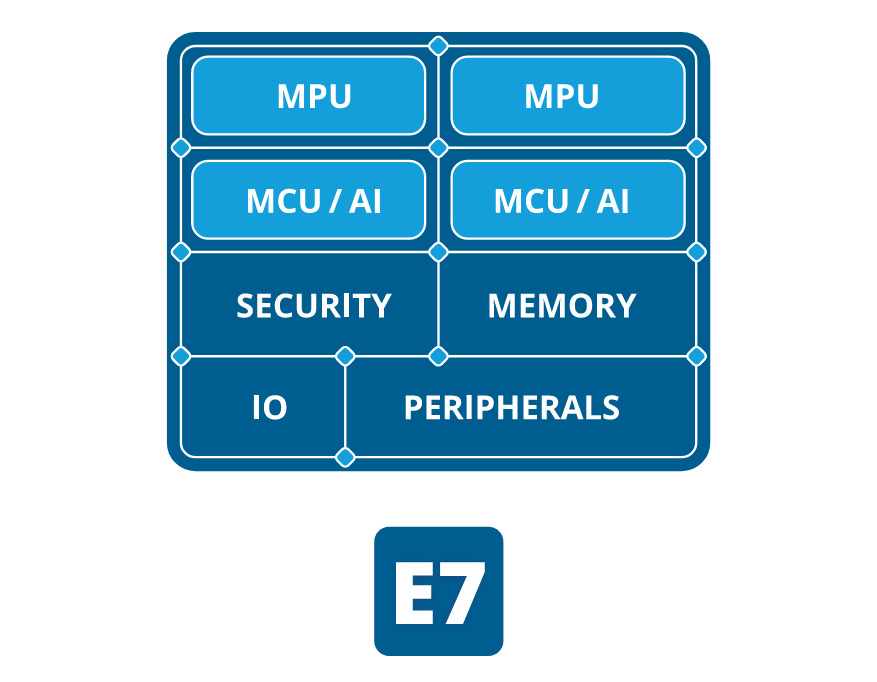

Alif Ensemble Cortex-A32 & Cortex-M55 chips feature Ethos-U55 AI accelerator

Alif Semiconductor’s Ensemble is a family of processors and microcontrollers based on Arm Cortex-A32 and/or Cortex-M55 cores, one or two Ethos-U55 AI accelerators, and plenty of I/Os and peripherals. Four versions are available as follows: Alif E1 single-core MCU with one Cortex-M55 core @ 160 MHz, one Ethos U55 microNPU with 128 MAC/c Alif E3 dual-core MCU with one Cortex-M55 core @ 400 MHz, one Cortex-M55 core @ 160 MHz, one Ethos U55 with 256 MAC/c, one Ethos U55 with 128MAC/c Alif E5 triple-core fusion processor with one Cortex-A32 cores @ 800 MHz, one Cortex-M55 core @ 400 MHz, one Cortex-M55 core @ 160 MHz, one Ethos U55 with 256 MAC/c, one Ethos U55 with 128MAC/c Alif E7 quad-core fusion processor with two Cortex-A32 cores @ 800 MHz, one Cortex-M55 core @ 400 MHz, one Cortex-M55 core @ 160 MHz, one Ethos U55 with 256 MAC/c, one Ethos U55 with […]

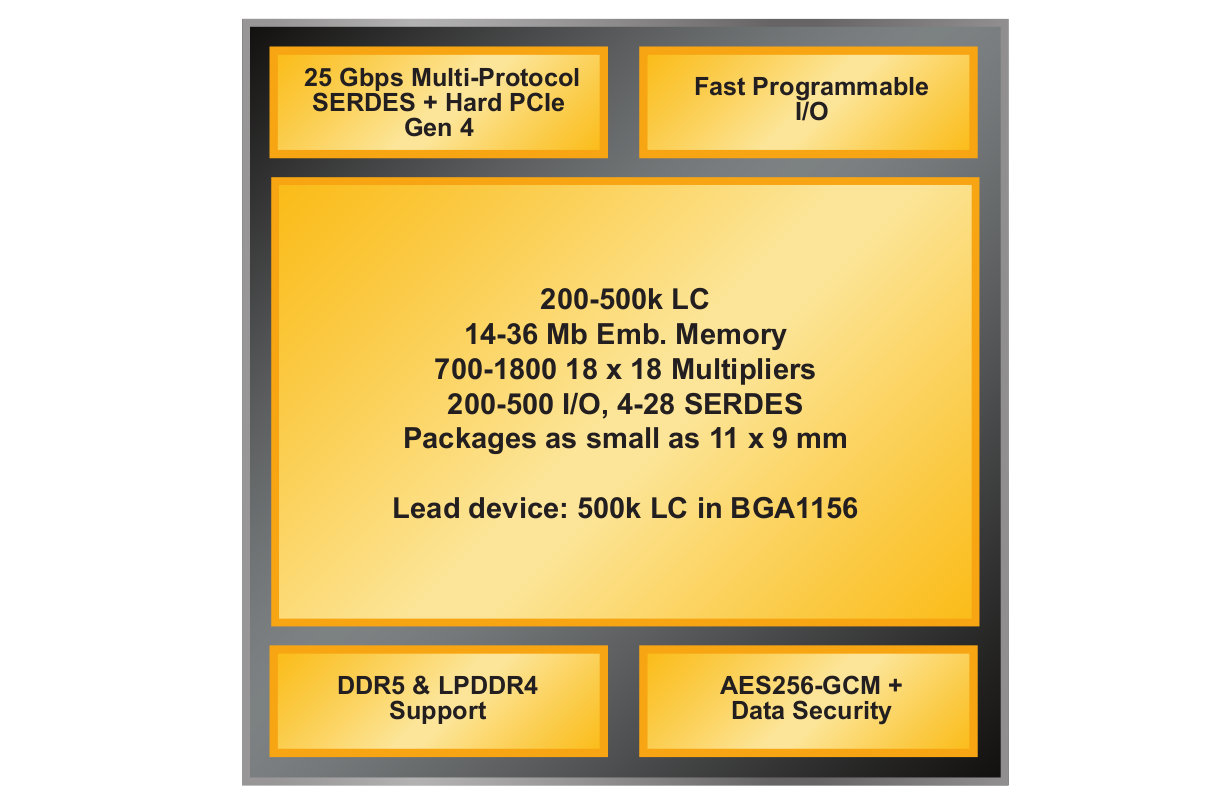

Lattice Avant mid-range FPGA platform features up to 500K logic cells, 25 Gbps SERDES, Hard PCIe Gen4

Lattice Avant is a new low-power and small form factor mid-range FPGA platform, manufactured with a 16nm FinFET process, and equipped with 25 Gb/s SERDES, hardened PCI Express, external memory PHY interfaces, a high DSP count, and a security engine. Lattice Semi is better known for its entry-level FPGAs such as the iCE40 which is popular in the community thanks to low-cost hardware and support for open-source tools, but the Avant platform marks the company’s entry into the mid-range FPGA market, defined by chips with 100k to 500k logic cells (LCs). Lattice Avant highlights: FPGA fabric – 200K to 500K logic cells up to 350 MHz DSP – 700 to 1,8000 18×18 multipliers @ up to 650 MHz to support the latest AI algorithms Memory 14-36 Mbit embedded memory up to 650 MHz DDR3L/DDR4/LPDDR4 and DDR5 support I/Os 4x to 28x 25 Gbps multi-protocol SERDES Hard PCIe Gen4 200 to […]