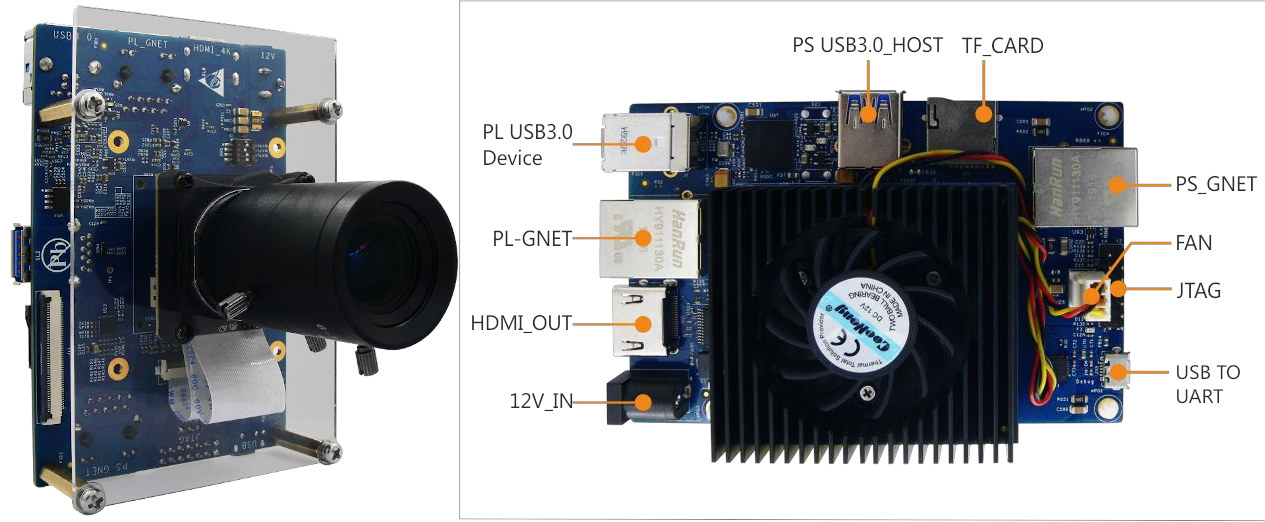

Last year, MyIR Tech introduced MYD-CZU3EG development board powered by a Xilinx Zynq UltraScale+ ZU3EG MPSoC with Arm Cortex-A53 cores and FPGA fabric designed for applications such as cloud computing, machine vision, flight navigation, and other complex embedded applications. The company has now announced another Zynq Ultrascale+ ZU3EG based platform dedicated to machine vision. The VECP Starter Kit (Vision Edge Computing Platform) is comprised of MYD-CZU3EG-ISP development board fitted with the company’s MYC-CZU3EG Zynq UltraScale+ MPSoC CPU module, a fansink, and a SONY IMX334 4K camera sensor. MYD-CZU3EG-ISP development board specification: MYC-CZU3EG SoM MPSoC – Xilinx Zynq UltraScale+ XCZU3EG-1SFVC784E (ZU3EG, 784 Pin Package) MPSoC with quad-core Arm Cortex-A53 processor @ 1.2 GHz, dual-core Cortex-R5 processor @ 600 MHz, Arm Mali-400MP2 GPU, and 16nm FinFET+ FPGA fabric (154K logic cells, 7.6 Mb memory, 728 DSP slices) System Memory – 4GB DDR4 @ 2,400MHz Storage – 4GB eMMC Flash, 128MB QSPI Flash […]

NetBSD 9.0 Released with Aarch64 Support, Arm ServerReady Compatibility

Yesterday, we wrote about Raspberry Pi 4 getting UEFI+ACPI firmware for Arm SSBR compliance allowing the board to run operating systems designed for “Arm ServerReady” servers out of the box. NetBSD 9.0 was just released on February 14, 2020, with support for Aarch64 (64-bit Arm) which had been in the works for a few years, and includes support for “Arm ServerReady” compliant machines (SBBR+SBSA). NetBSD 9.0 main changes related to hardware support: Support for AArch64 (64-bit Armv8-A) machines Compatibility with “Arm ServerReady” compliant machines (SBBR+SBSA) using ACPI. Tested on Amazon Graviton and Graviton2 (including bare metal instances), AMD Opteron A1100, Ampere eMAG 8180, Cavium ThunderX, Marvell ARMADA 8040, QEMU w/ Tianocore EDK2 Symmetric and asymmetrical multiprocessing support (big.LITTLE) Support for running 32-bit binaries via COMPAT_NETBSD32 on CPUs that support it Single GENERIC64 kernel supports ACPI and device tree based booting Supported SoCs Allwinner A64, H5, H6 Amlogic S905, S805X, S905D, […]

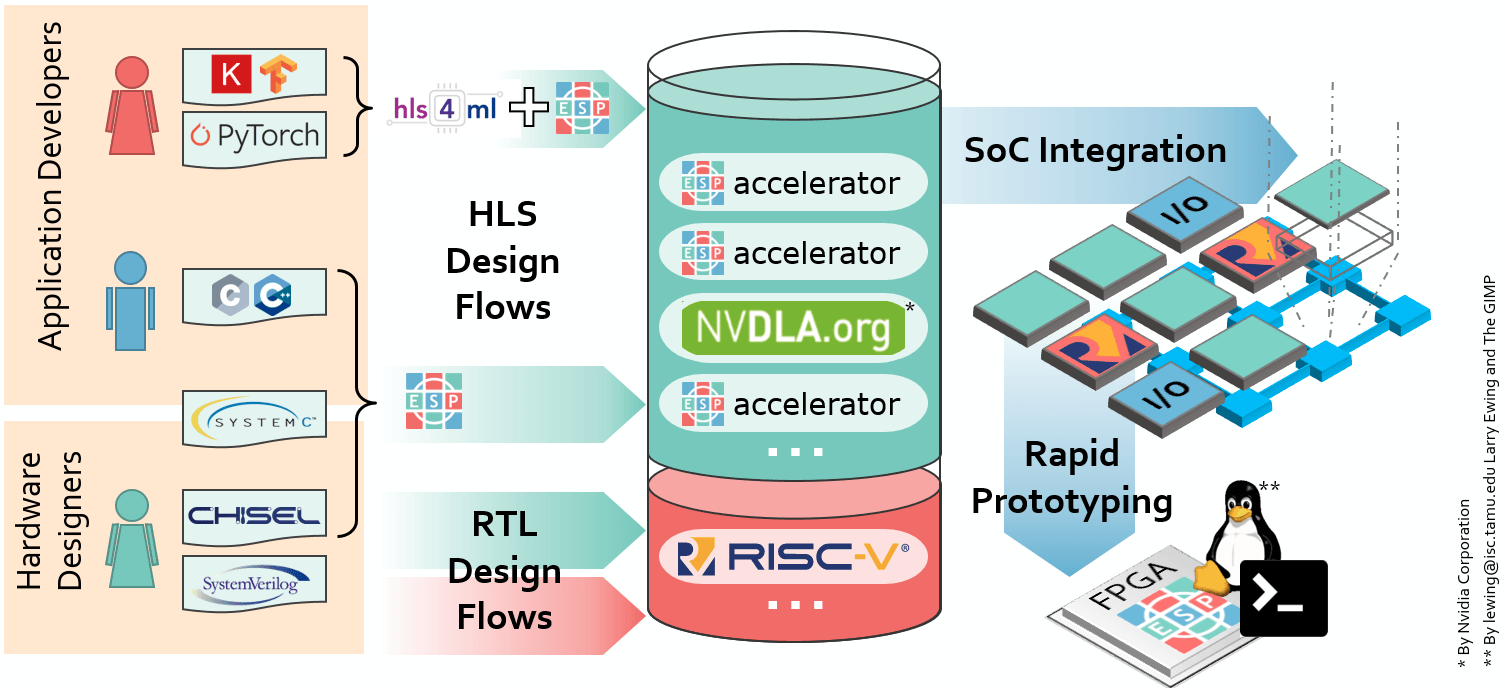

ESP Open Source Research Platform Enables the Design of RISC-V & Sparc SoC’s with Accelerators

FOSDEM 2020 will take place next week, and there will be several interesting talks about open-source hardware and software development. One of those is entitled “Open ESP – The Heterogeneous Open-Source Platform for Developing RISC-V Systems” with an excerpt of the abstract reading: ESP is an open-source research platform for RISC-V systems-on-chip that integrates many hardware accelerators. ESP provides a vertically integrated design flow from software development and hardware integration to full-system prototyping on FPGA. For application developers, it offers domain-specific automated solutions to synthesize new accelerators for their software and map it onto the heterogeneous SoC architecture. For hardware engineers, it offers automated solutions to integrate their accelerator designs into the complete SoC. If we go to the official website, we can see ESP (Embedded Scalable Platform) actually supports both 32-bit Leon3 (Sparc) and 64-bit Ariane (RISC-V) cores, and various hardware accelerators from the platform or third parties. Highlights: […]

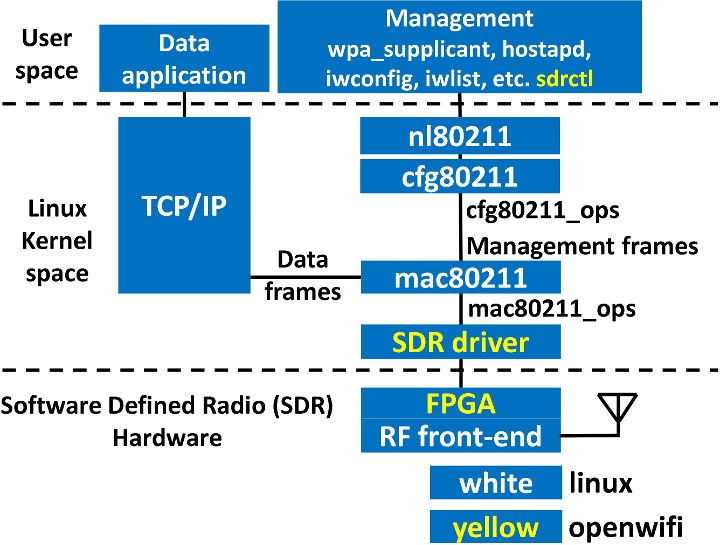

OpenWiFi Open-Source Linux-compatible WiFi Stack Runs on FPGA Hardware

WiFi is omnipresent on most connected hardware, and when it works it’s great, but when there are issues oftentimes they can not be solved because the firmware is a closed-source binary. I understand companies do that either to protect their IP and/or make sure end-users do not break FCC compliance. OpenWiFi project aims to deliver a completely open-source SDR (Software Defined Radio) WiFi implementation compatible with Linux and running on FPGA hardware. OpenWiFi currently supported features: 802.11a/g; 802.11n MCS 0~7; 20MHz Mode tested: Ad-hoc; Station; AP DCF (CSMA/CA) low MAC layer in FPGA Configurable channel access priority parameters: duration of RTS/CTS, CTS-to-self SIFS/DIFS/xIFS/slot-time/CW/etc Time slicing based on MAC address Easy to change bandwidth and frequency: 2MHz for 802.11ah in sub-GHz 10MHz for 802.11p/vehicle in 5.9GHz The developers tested OpenWiFi on Xilinx ZC706 FPGA evaluation kit coupled Analog Devices fmcomms2/fmcomms4 RF board to form an access point, and connected it to […]

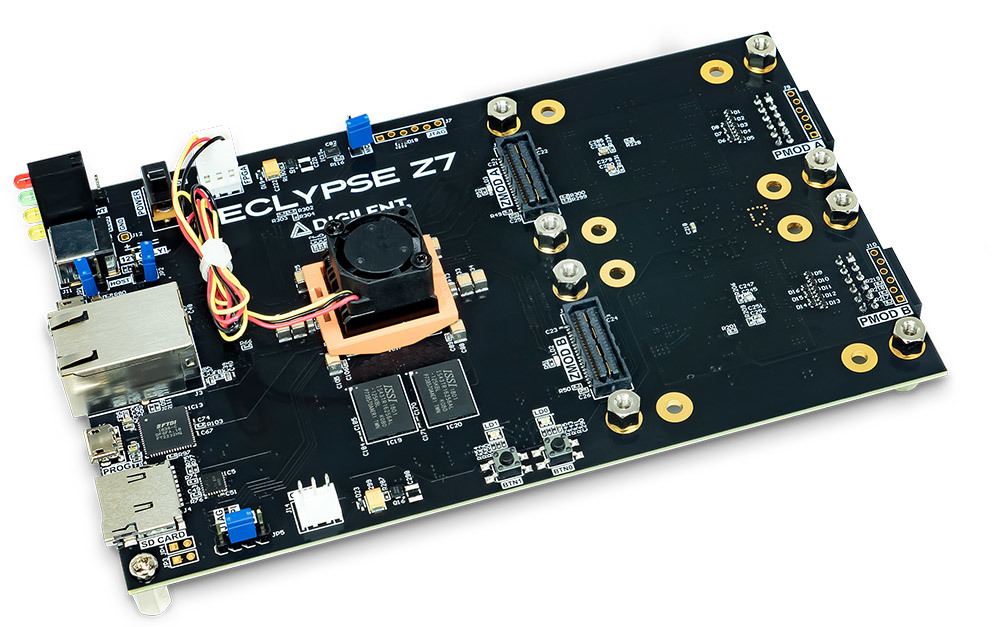

Digilent Offers 2 Zynq-Based Linux Development Boards Supporting SYZYGY Expansion

Digilent Announces SYZYGY high-speed SBCs Digilent has announced two new SBCs that are ultra-high-speed and built to be more modular than its other boards. The company, which has a great deal of experience in Pmod lower speed FPGA standards has now entered the open-source, SYZYGY high-speed standards with its Eclypse Z7 and the Genesys ZU development SBCs. Background on the Digilent Zybo FPGA SoC SBC We reported on the Zybo development board FPGA SoC from Digilent and that seems to have lead to the latest format for the Eclypse Z7. Zmod There is also a release planned for the new Zmod modules, built to work with both the Eclypse Z7 and the Genesys ZU as SYZYGY compliant expansion modules. Opal Kelly and Zmod expansion The Zmods are Opal Kelly module standard, called SYZYGY, first seen in the Opal Kelly SYZYGY Brain-1 SBC. The standard was developed to jump the gap […]

Linaro Connect San Diego 2019 Schedule – IoT, AI, Optimizations, Compilers and More

Linaro has recently released the full schedule of Linaro Connect San Diego 2019 that will take place on September 23-27. Even if you can’t attend, it’s always interested to check out the schedule to find out what interesting work is done on Arm Linux, Zephyr OS, and so on. So I’ve created my own virtual schedule with some of the most relevant and interesting sessions of the five-day event. Monday, September 23 14:00 – 14:25 – SAN19-101 Thermal Governors: How to pick the right one by Keerthy Jagadeesh, Software Engineer, Texas Instruments With higher Gigahertz and multiple cores packed in a SoC the need for thermal management for Arm based SoCs gets more and more critical. Thermal governors that define the policy for thermal management play a pivotal role in ensuring thermal safety of the device. Choosing the right one ensures the device performs optimally with in the thermal budget. […]

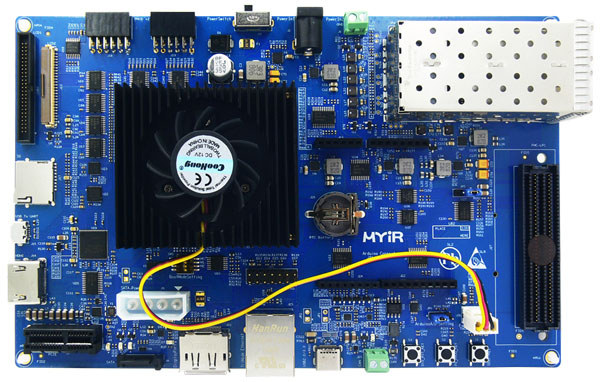

MYIR Announces Xilinx Zynq UltraScale+ MPSoC SoM and Development Board

MYIR Technology has been selling Xilinx Zynq-7000 FPGA + Arm systems-on-module since 2016, but the Chinese company has now announced new modules based on the more powerful Xilinx Zynq Ultrascale+ MPSoC with Arm Cortex-A53 cores, Arm Cortex-R5 cores, and Ultrascale FPGA fabric, as well as a corresponding development board. MYC-CZU3EG Zynq UltraScale+ MPSoC CPU Module CPU module specifications: MPSoC – Xilinx Zynq UltraScale+ XCZU3EG-1SFVC784E (ZU3EG, 784 Pin Package) MPSoC with quad-core Arm Cortex-A53 processor @ 1.2 GHz, dual-core Cortex-R5 processor @ 600 MHz, Arm Mali-400MP2 GPU, and 16nm FinFET+ FPGA fabric (154K logic cells, 7.6 Mb memory, 728 DSP slices) System Memory – 4GB DDR4 @ 2,400MHz Storage – 4GB eMMC Flash, 128MB QSPI Flash On-module chips Gigabit Ethernet PHY USB PHY Intel Power Module Clock Generator 2x Samtec 0.5mm pitch 160-pin high-speed headers bringing out Networking – Gigabit Ethernet USB – USB 2.0 interface 4x PS GTR transceivers along with […]

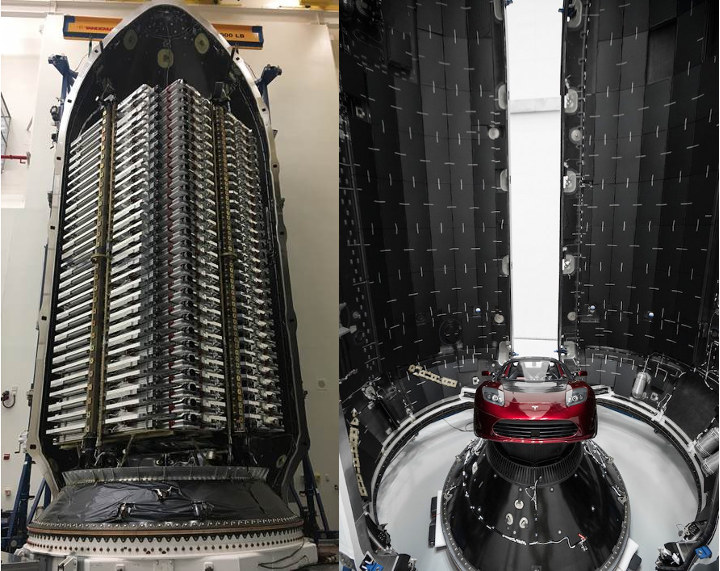

Xilinx Arm FPGA, Snapdragon SoM’s, and Wandboard SBC Field Trip to Space

Most embedded systems are used here on planet earth, but some do take off heading for space, and this week I come accross two separate projects leveraging Arm processors and FPGAs, as well as Ubuntu/ROS and Android operating systems: SpaceX Starlink communication satellites and Astrobee robots roaming in the international space station (ISS) SpaceX Starlink Satellites with Xilinx Ultrascale+ Arm + FPGA SoC SpaceX is about to launch a cloud of 60 Starlink communication satellites that aims to provide internet communication anywhere in the world. That’s just a start as eventually the plan is to get up to 12,000 of those satellites. Usually, we would not know many technical details about the satellites, but as one reader pointed out (Thanks Lawrence!), a Reddit thread about the launch, also pointed to a NASA document revealing the satellites are powered by Xilinx Ultrascale+ quad core Cortex-A53 processor with FPGA fabric. Milestone 2 […]