MYIR, the Chinese based company that has developed several ARM-based hardware solutions, has introduced a new SoM powered by the ST’s STM32MP1 microprocessor called the MYC-YA157C CPU Module with an accompanying development board known as the MYD-YA157C development board. Early last year, STMicro announced the introduction of the STM32MP1, the first STM32 MPU (Microprocessor Unit) that features one or two Arm Cortex-A7 cores running Linux, as well as an Arm Cortex-M4 real-time core making it possible to use previous STM32 codes on the new unit. Although, less than 1-year-old, the STM32MP1 microprocessor has since be deployed on a couple of development boards like the STMicro’s own discovery kits and evaluation platform, Emtrion emSBC-Argon, PanGu single-board computer, and even octavo systems unveiled the OSD32MP15x system-in-package. One primary observation with these other developments boards is their relatively steep cost, and something MYIR aims to address. MYiR MYC-YA157C STM32MP1 CPU Module The MYC-YA157C […]

STMicro STM32MP1 Cortex A7/M4 MPU Supports Linux and Android

When Linux 4.17 was released last June, we discovered an interesting new STM32 part: STM32MP157C dual core Cortex-A7 processor. It was the first time I saw an STM32 IC not based on Arm Cortex-M microcontroller core, but we knew only very little details at the time. STMicro has now made it official, and introduced STM32MP1, the first STM32 MPU (Microprocessor Unit) that features one or two Arm Cortex-A7 cores running Linux, as well as an Arm Cortex-M4 real-time core that allows to re-use code from existing STM32 projects. STM32MP1 key features and specifications: Cores Single or Dual Cortex-A7 core(s) running at 650 MHz with 32-Kbyte L1 Instruction cache, 32-Kbyte L1 Data cache, 256-Kbyte Level 2 cache Cortex-M4 core running at 209 MHz with single-precision floating point unit (FPU), digital signal processor (DSP) instructions, and memory protection unit (MPU) GPU (STM32MP157 only) – Vivante 3D GPU with OpenGL ES 2.0 support; […]

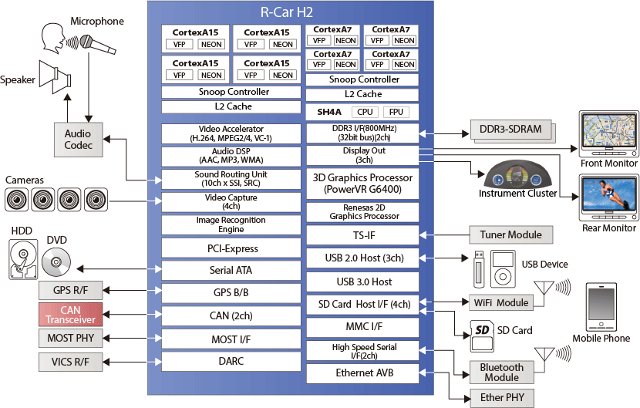

Renesas R-Car H2 is an Octo Core big.LITTLE Processor for Your Car

Renesas announced a new automotive SoC called the R-Car H2 that features 4 Cortex-A15 cores together with 4 Cortex A7 cores (optional) in big.LITTLE configuration, as well as an Imagination PowerVR Series6 G6400 GPU. This SoC can optionally come with Renesas SH-4A, a real-time processing CPU core acting as a multimedia engine (MME) , and Renesas’ IMP-X4 core, a real-time image processing unit that enables developers to implement augmented reality application such as 360-degree camera views and image recognition. This Renesas processor is a multimedia power house, as it can handle 4x 1080p video en/decoding, including Blu-Ray support at 60 frames per second, as well as image/voice recognition and high-resolution 3D graphics with virtually no CPU usage. Here are R-Car H2’s specifications provided on Renesas website: Product number R8A7790x Power supply voltage 3.3/1.8 V (IO), 1.5/1.35 V (DDR3), 1.0 V (Core) CPU core ARM Cortex-A15 Quad ARM Cortex-A7 Quad (device […]

ARM big.LITTLE Processing Demo (HMP) on ARM TC2 Test Chip

Samsung launched Exynos 5 Octa at CES 2013. This processor comes with 8 cores: 4 Cortex A15 cores and 4 Cortex A7 cores, and it’s the first processor that’s been announced to work in big.LITTLE configuration, where the big cores (A15) handle demanding tasks, and the LITTLE cores (A7) handle simpler tasks such as audio playback or background tasks. This is all done to optimize power consumption. There are 2 big.LITTLE software implementations: In-kernel switcher (IKS) and heterogeneous multi-processing (HMP). The first one is easier to implements but can only use 4 cores (in Exynos 5 Octa) at a time, and the second is more complex, but can handle all 8 cores, and assign individual tasks to a particular core. For more technical details about big.LITTLE implementations, you can read my previous post. ARM and Samsung recently uploaded a video providing an overview of big.LITTLE (but instead of IKS and […]

MediaTek Unveils Quad-Core Cortex-A7 MT6589 SoC

This December is a busy month for silicon manufacturers and Cortex A7 processor, after AllWinner A20 and A31, Rockchip RK3188 (4x Cortex A9), Qualcomm MSM8226 & MSM8626, Broadcom BCM21664T (2x Cortex A9), MediaTek announced MT6589, a quad-core Cortex A7 System on a Chip (SoC) with Imagination Technologies PowerVR Series5XT GPU that targets mid to high-end Android smartphones and tablets. Mediatek MT6589 also integrates a multi-mode UMTS Rel. 8/HSPA+/TD-SCDMA modem developed in-house, Mediatek’s 4-in-1 connectivity combo (802.11n Wi-Fi, BT4.0, GPS and FM), and a multimedia subsystem that supports 1080p 30fps/30fps low-power video playback and recording, a 13MP Camera with Integrated ISP, up to FHD (1920×1080) LCD displays, and enhanced picture processing for DTV-grade image quality. This SoC also features MediaTek’s “Cool 3D” suite for support for stereo 3D cameras and displays & real-time 2D-to-3D, as well as support for Miracast technology. The first devices based on MediaTek MT6589 should be available […]

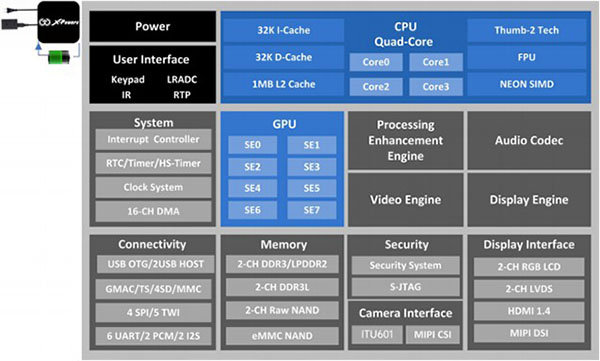

AllWinner Publishes A31 and A20 Processors Details

Several tablets based on AllWinner A31 quad core processor have been announced this week, such as Onda V972, but we did not really have full details on the processor. We now know more since AllWinner added product pages for two new (sun6i architecture. [Edit: A20 is actually sun7i…]) processors: AllWinner A31 and AllWinner A20. AllWinner A31 Specifications AllWinner A31 is a quad core Cortex A7 processor with PowerVR SGX544MP2 GPU (8 shader engines). CPU – ARM Cortex-A7 Quad-Core with 256KB L1-Cache/1MB L2-Cache GPU – POWER VR SGX 544 with Eight logic cores. Open GL ES2.0, Open CL1.x and DX 9_3 compliant. Memory – Dual-Channel LPDDR2/DDR3/DDR3L Controller, Dual-Channel NAND FLASH Controller and 64-bit ECC Video UHD H.264 4K ×2K @30fps video decoding Full HD video decoding BD Directory, BD ISO and BD m2ts video decoding H.264 High Profile 1080P@60fps encoding 3840×1080@30fps 3D decoding Complies with RTSP, HTTP, HLS, RTMP, MMS streaming […]

Qualcomm Announces SnapDragon S4 MSM8226 & MSM8626 Quad Core Cortex A7 Processors

After news of an AllWinner A31 Tablet earlier today, here’s an other quad core Cortex A7 processor announcement, as Qualcomm has recently added of 2 new chipsets to its Snapdragon S4 family of mobile processors: the MSM8226 and MSM8626 featuring 4 ARM Cortex A7 core and Adreno 305 GPU. The processors support 1080p video playback and up to 13MP cameras. Both processors are built using 28nm technology node, and will be ready for customer sampling by Q2 2013 for UMTS, CDMA and TD-SCDMA. These 2 chipsets will incorporate WTR2605, a new multi-mode radio transceiver, specifically designed and optimized to address China requirements such as support for TD-SCDMA, CDMA 1xAdv and HSPA+. The WTR2605 transceiver comes with an integrated, high-performance GPS core with GLONASS and Beidou support, and is said to offer 40 percent power savings and 60 percent smaller footprint compared to previous generations. The company will also provide Qualcomm […]

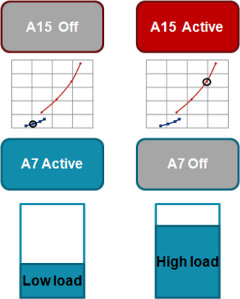

Big.LITTLE Processing Implementations and Current Status

There was a big,LITTLE mini-summit during Linaro Connect Europe 2012, where an update was given on current big.LITTLE implementations and the results of measurement of power vs performance. Big.LITTLE Processing Implementations Overview As briefly mentioned in “Versatile Express TC2 (2xA15, 3xA7) Development Board at ARM Techcon 2012“, there are 2 big.LITTLE implementations: In-kernel switcher (IKS) This implementation is already available through Linaro and only required minimal changed to the kernel as it mainly an augmentation to DVFS (Dynamic Voltage and Frequency Scaling) except instead of only adjusting voltage and frequency depending on the load, it will also move the load to different cores. The main drawback is that this implementation only uses half the cores. For example, on a 2x Cortex A15 / 2x Cortex A7 system, it can only use 2 cores at the same time (either A15 or A7 cores), as the load is managed between one type […]