FOSDEM – which stands for Free and Open Source Software Developers’ European Meeting – is a free-to-participate event where developers meet on the first week-end of February to discuss open source software & hardware projects. FOSDEM 2019 will take place on February 2 & 3, and the schedule has already been published with 671 speakers scheduled to speak in 711 events themselves sorted in 62 tracks. Like every year, I’ll create a virtual schedule based on some of the sessions most relevant to this blog in tracks such as open hardware, open media, RISC-V, and hardware enablement tracks. February 2 10:30 – 10:55 – VkRunner: a Vulkan shader test tool by Neil Roberts A presentation of VkRunner which is a tool to help test the compiler in your Vulkan driver using simple high-level scripts. Perhaps the largest part of developing a modern graphics driver revolves around getting the compiler to […]

Fomu FPGA board fits inside a USB port, Supports Python, RISC-V Softcore

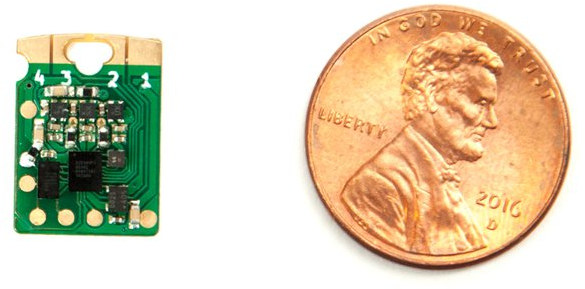

Sutajio Ko-usagi launched Tomu, a tiny open source hardware USB board that fits inside a USB port at the very beginning of this year. The company is back with a similarly shaped board, but instead of featuring a Silicon Labs EFM32 Arm Cortex-M0+ microcontroller, Fomu is equipped with a Lattice ICE40 UltraPlus FPGA. Fomu specifications: FPGA – Lattice ICE40UP5K FPGA with 5280 logic cells System Memory – 128 kB RAM for a soft CPU Storage – 1 or 2 MB SPI flash Clock – 48 MHz crystal oscillator USB – 1x USB 2.0 FS (12 Mbps) port Misc – 4x buttons, 1x RGB LED The default Fomu firmware exposes a USB bootloader running a RISC-V softcore, and the platform is powerful enough to run a port of Python. It’s also possible to experiment with LM32 and OpenRISC softcores on the platform. Using the board is pretty straightforward as just you […]

Bluespec Flute is a 5-Stage Open Source RISC-V Processor

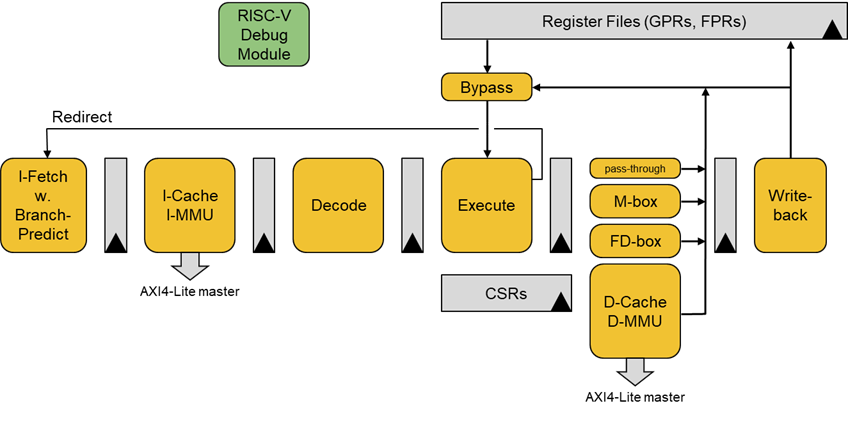

Bluespec is a US company that provides RISC-V processors and development tools that “speed integration, debugging and verification of embedded systems”. Their first RISC-V release was the Piccolo 3-stage in-order processor targeting low end embedded systems and IoT applications. The company has now announced Bluespec Flute a 5-stage in-order open source RISC-V processor with the release of a synthesizable Verilog for a bare metal RV32IMA core and a supervisor level RV64IMA core. Bluespec Flute key features: RV32IMU with ‘M’ extension (integer multiply/divide) RV64IMASU with ‘A’ extension (atomic memory ops) and ‘M’ extension (integer multiply/divide) AXI4-Lite interface 5-stage pipeline 100 MHz (Xilinx UltraScale) < 5000 LUTs (Xilinx UltraScale) 4KB Instruction & Data caches Hardware multiply-divide RISC-V Debug Module You’ll find the source code in BSV (Bluespec SystemVerilog) and instructions to get started in Github. Bluespec Flute core has been tested in Xilinx UltraScale/UltraScale+ boards so far. In the future, the company […]

BOOM Open Source RISC-V Core Runs on Amazon EC2 F1 Instances

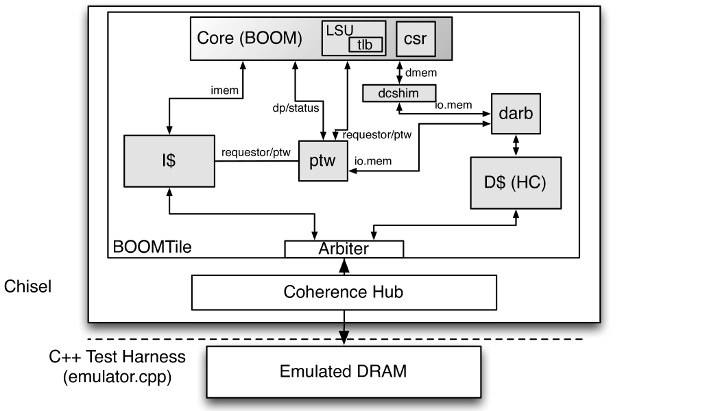

The Berkeley Out-of-Order Machine (BOOM) is an open source RV64G RISC-V core written in the Chisel hardware construction language, and mainly ASIC optimized. However, it is also usable on FPGAs, and developers support the FireSim flow to run BOOM at over 90 MHz on Xilinx Ultrascale+ FPGAs found in Amazon EC2 F1 instances. The BOOM core was created at the University of California, Berkeley in the Berkeley Architecture Research group, in order to create a high performance, synthesizable, and parameterizable core for architecture research. Key features of BOOM core: ISA – RISC-V (RV64G) Synthesizable FPGA support Parameterized Floating Point (IEEE 754-2008) Atomic Memory Op Support Caches & Virtual Memory Boots Linux Privileged Arch v1.11 External Debug BOOM is said to be inspired by the MIPS R10k and the Alpha 21264 out–of–order processors, based on a unified physical register file design (aka as “explicit register renaming”). The source code for the […]

MicroSemi Introduces PolarFire FPGA & RISC-V SoC

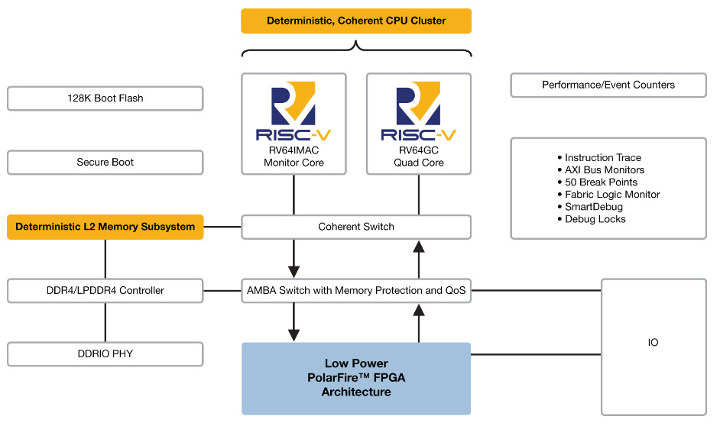

In the past we’ve covered SoCs comprised of Arm cores and FPGA fabric via Xilinx Zynq-7000 series SoCs and Zynq UltraScale+ series MPSoCs, respectively featuring up to two Arm Cortex A9 cores, and up to four Cortex A53 cores. MicroSemi has now announced an alternative, not based on Arm cores, but instead based on SiFive U54-MC RISC-V cores combined with PolarFire FPGA fabric. PolarFire FPGA RISC-V SoC key features & specifications: FPGA – Microsemi PolarFire FPGA Processor Cores – Up to 4x SiFive U54-MC RISC-V cores clocked at up to 1.5GHz (performance similar to Cortex-A35 cores); 28nm process Deterministic Coherent Multi-core CPU Cluster Deterministic L2 Memory Subsystem System Memory I/F – Integrated DDR4/LPDDR4 Controller and PHY Storage – Secure Boot, 128K Boot Flash Debug capability Rich I/Os Low Power – Low static power; power optimized transceivers, up to 50% lower power compared to SRAM based FPGAs So we don’t have […]

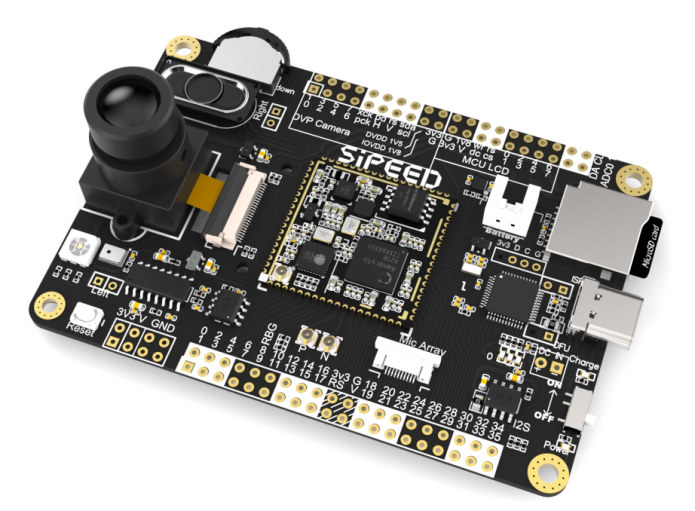

MAIX Development Boards with Sipeed M1 RISC-V AI Module Launched for $5 and Up (Crowdfunding)

Sipeed M1 (aka MAIX-I)is a compact module based on Kendryte K210 dual core RISC-V processor designed for low power artificial intelligence workloads at the edge, such as face detection, object recognition, or audio processing. The module and some development boards are available on Taobao for the Chinese market, as well as YOYCart for the rest of the world, but the company has now launched several MAIX boards based on M1 module through an Indiegogo campaign with price starting at just $5 a piece. Sipeed MAIX Bit (aka MAIX Micro) is the cheapest one at $5 (early bird) / $6 with the following specifications: SoC – Kendryte K210 dual core 64-bit RISC-V processor @ 400 MHz (overclockable up to 800 MHz) with KPU CNN hardware accelerator APU audio hardware accelerator with support for up to 8 mics, up to 192 KHz sample rate FPIOA (Field Programmable IO Array) mapping 255 functions to […]

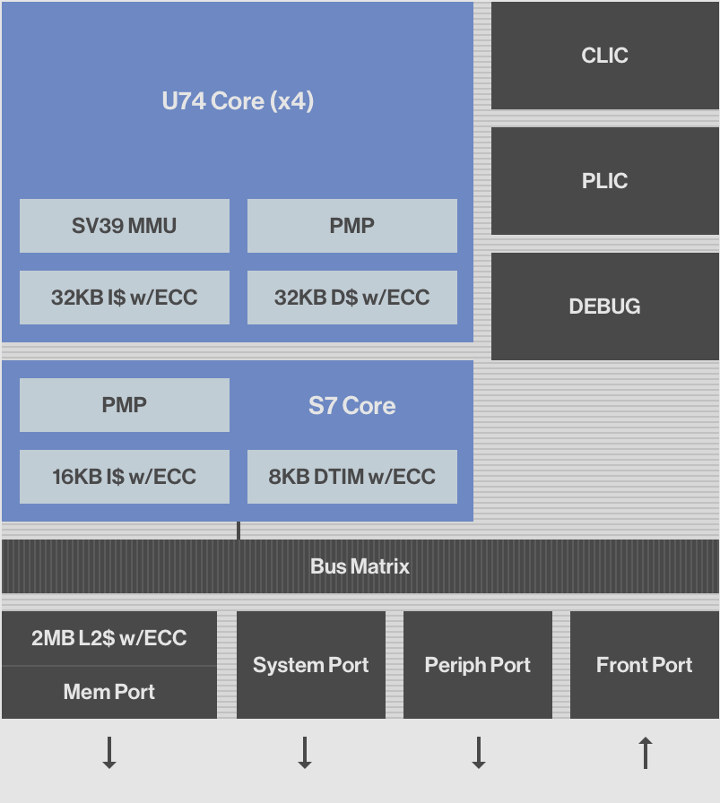

SiFive Introduces 7 Series RISC-V Cores with E7, S7 and U7 series

SiFive has recently announced their Core IP 7 Series of RISC-V cores offering better performance, and designed to enable “embedded intelligence” in applications such as 5G, networking, storage, augmented reality, artificial intelligence, SLAM, and sensor fusion. Three families of the new 7 Series been launched with namely SiFive E7, S7 and U7 Core IP Series, so let’s have a look at each of them. E7 Core IP Series – E76 and E76-MC Cores The E7 Core IP Series comprises the 32-bit E76 and E76-MC (Multi-core), provides hard real-time capabilities, and compares to Arm’s Cortex M7, Cortex-R7/R8 cores. E76-MC Key Features Fully compliant with the RISC-V ISA specification 4x RV32IMAFC E76 Cores Machine and User Mode Support In-order, 8-stage pipeline Advanced Memory Subsystem 32KB Instruction Cache 32KB Instruction Tightly Integrated Memory (ITIM) 32KB Data Cache 32KB FIO RAM 256KB L2 Cache High-performance TileLink Interface Benchmark Scores- 2.3 DMIPS/MHz, 4.9 CoreMark/MHz E76 […]

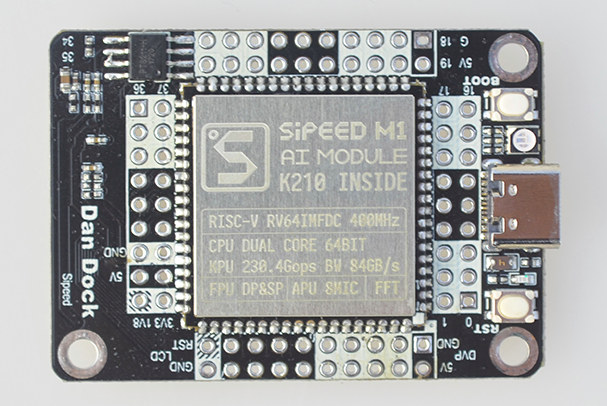

Sipeed M1 RISC-V Computer Vision Module Features Kendryte K210 Processor

Just a few days ago, I wrote about Kendryte KD233 board featuring Kendryte K210 dual core RISC-V processor, with some fairly detailed documentation, public links to toolchains and other tools. and going for $50. But the team behind LicheePi boards informed me that they also made their own K210 module called Sipeed M1 and selling on Taobao for the Chinese market, as well as on Yoycart for $10.89 plus shipping for the oversea market, and you’ll find a devkit with a dock board for about $24 and up depending on options. Sipeed M1 module specifications: SoC – Kendryte K210 dual core 64-bit RISC-V processor @ 400 MHz with KPU CNN hardware accelerator, APU audio hardware accelerator, 6 MB general purpose SRAM, 2MB AI SRAM memory, and AXI ROM to load user program from SPI flash Package – 72-pin (25.4 x 25.4mm) But you’ll probably want to get start with M1 […]