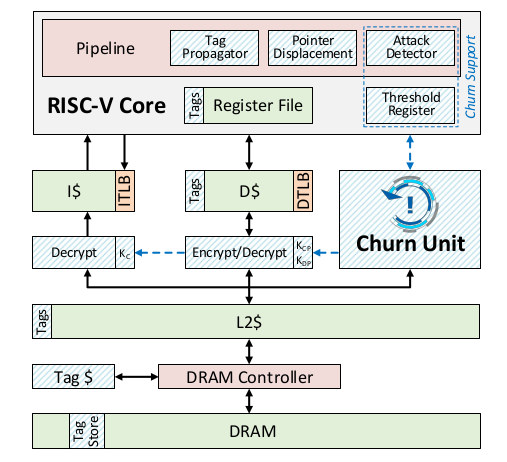

Code gets continuously written and updated for new features, optimizations and so on. Those extra lines of code sometimes come at a cost: a security bug gets inadvertently introduced into the code base. The bug eventually gets discovered, a report is filled, and a software fix is committed to solve the issue, before the new software or firmware to push to the end user. This cycle repeats ever and ever, and this means virtually no software or device can be considered totally secure. The University of Michigan has developed a new processor architecture called MORPHEUS, and that blocks potential attacks by encrypting and randomly reshuffling key bits of its own code and data several times per second through a “Churn Unit”. The new RISC-V based processor architecture does not aim to solve all security issues, but focuses specifically on control-flow attacks made possible for example by buffer overflows: Attacks often […]

Linux 5.1 Release – Main Changes, Arm, MIPS & RISC-V Architectures

Linus Torvalds has just announced the release of Linux 5.1: So it’s a bit later in the day than I usually do this, just because I was waffling about the release. Partly because I got some small pull requests today, but mostly just because I wasn’t looking forward to the timing of this upcoming 5.2 merge window. But the last-minute pull requests really weren’t big enough to justify delaying things over, and hopefully the merge window timing won’t be all that painful either. I just happen to have the college graduation of my oldest happen right smack dab in the middle of the upcoming merge window, so I might be effectively offline for a few days there. If worst comes to worst, I’ll extend it to make it all work, but I don’t think it will be needed. Anyway, on to 5.1 itself. The past week has been pretty calm, […]

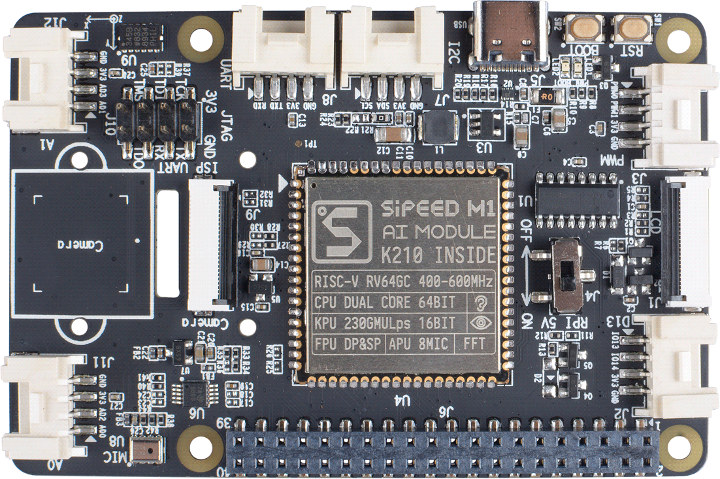

Grove AI HAT Helps Raspberry Pi Run Edge Computing Workloads

Last year we wrote about Kendryte K210 dual core RISC-V processor specifically designed for for machine vision and machine hearing as well as the corresponding Kendryte KD233 which enables inference at the edge, e.g. tasks such as face recognition or object detection. Latter on we found the processor in Sipeed M1 module which went for as low as $5 in a crowdfunding campaign, and was fitted to some low cost boards now selling for $12.90 on Seeed Studio. The latter company has now designed Grove AI HAT that aims to assist Raspberry Pi in running the edge computing workloads previously described, as exposes 6 Grove interfaces to extend functionality with some of the Grove add-on modules. Grove AI HAT specifications: AI Module – Sipeed “MAIX” M1 with Kendryte K210 dual core RISC-V processor @ 600 MHz, KPU Convolutional Neural Network (CNN) hardware accelerator, APU audio hardware accelerator, 8 MB general […]

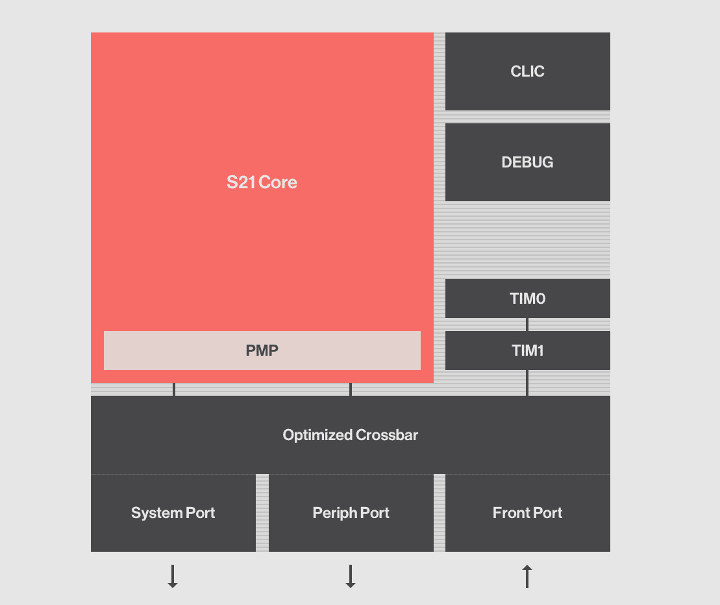

SiFive S2 RISC-V Core may be the World’s Smallest 64-bit Embedded Core

Last year, SiFive introduced their first RISC-V cores competing with Arm Cortex-R family of processors thanks to their S7 Series 64-bit RISC-V Core IP providing an answer to Arm Cortex-R7/R8 32-bit real-time processors. The company has now announced the SiFive S2 RISC-V core that it claims to be the world’s smallest 64-bit embedded core, and also the first SiFive IP core without any direct competitive equivalent in the market. For now, there’s only one core in the family with SiFive S21 offering the following key features: RISC-V ISA – RV64IMAC 64-bit AXI Ports Machine and User Mode with 4 Region Physical Memory Protection 3-stage pipeline with Simultaneous Instruction and Data Access 2 Banks of Tightly Integrated Memory (TIM) CLIC (Core Local Interrupt Controller) with 127 interrupts Advanced debug with 4 hardware breakpoints/watchpoints Performance – 1.6 DMIPS/MHz; 3.2 Coremarks/MHz The company compares its to the SiFive S5 cores, which I had […]

HiFive1 Rev B Board Gets FE310-G002 RISC-V Processor, WiFi & Bluetooth Module

SiFive launched what may have been the very first RISC-V development board in 2016 thanks to their HiFive1 Arduino compatible board powered by Freedom E310 (FE310) open source RISC-V processor. The company has now launched an upgrade version of the processor and board. Meet FE310-G002 processor and HiFive1 Rev B development board. HiFive1 Rev B development board specifications with new features highlighted in bold or stricken-through: MCU – SiFive Freedom E310-G0002 32-bit RV32IMAC processor @ up to 320+ MHz (1.61 DMIPS/MHz) Storage – 32 Mbit SPI flash (was 128 Mbit in the first version) Connectivity – ESP32-SOLO-1 WiFi & Bluetooth module I/Os 19x Digital I/O Pins 19x external interrupt pins 1x external wakeup pin 9x PWM pins 1/3 SPI Controllers/HW CS Pins I/O Voltages – 3.3V or 5V supported; note: bidirectional level shifters removed so FE310-G002 can drive the I/O pins directly at 3.3V only. USB – 1x micro USB […]

RISC-V Compliance Tests Aim to Address RISC-V Fragmentation

In the x86 world, one operating system image can usually run on all hardware thanks to clearly defined instruction sets, hardware and software requirements. Arm provides most flexibility in terms of peripherals, while having a fixed set of intrusions for a given architecture (e.g. Armv8, Armv7…), and this lead to fragmentation, so that in the past you had to customize your software with board files and other tweaks, and provide one binary per board, leading to lots of fragmentation. With device trees, things improved a bit, but there are still few images that will run on multiple boards without modifications. RISC-V provides even more flexibility that Arm since you can mess up with the instructions set with designers able to add or remove instructions as they see fit for their application. One can easily imagine how this can lead to a complete mess with binary code only running on a […]

FreeRTOS Kernel Now Supports RISC-V Architecture

FreeRTOS is one of the most popular operating systems found in embedded systems, and RISC-V open architecture is getting more and more traction, so it should come as no surprise that Amazon has now added RISC-V to their recently acquired FreeRTOS kernel. Jeff Barr, Chief Evangelist for AWS, explains both 32-bit and 64-bit RISC-V cores are supported, and several RISC-V boards are already supported out of the box: The kernel supports the RISC-V I profile (RV32I and RV64I) and can be extended to support any RISC-V microcontroller. It includes preconfigured examples for the OpenISA VEGAboard, QEMU emulator for SiFive’s HiFive board, and Antmicro’s Renode emulator for the Microchip M2GL025 Creative Board. There’s no a lot of information on Amazon announcement post, but FreeRTOS website has plenty of resources to help you get started with RISC-V. The page also lists some of the key features of the RISC-V port: Supports machine […]

Linux 5.0 Release – Main Changes, Arm, MIPS & RISC-V Architectures

Linus Torvalds has just released Linux 5.0: Ok, so the last week of the 5.0 release wasn’t entirely quiet, but it’s a lot smaller than rc8 was, and on the whole I’m happy that I delayed a week and did an rc8. It turns out that the actual patch that I talked about in the rc8 release wasn’t the worrisome bug I had thought: yes, we had an uninitialized variable, but the reason we hadn’t immediately noticed it due to a warning was that the way gcc works, the compiler had basically initialized it for us to the right value. So the same thing that caused not the lack of warning, also effectively meant that the fix was a no-op in practice. But hey, we had other bug fixes come in that actually did matter, and the uninitialized variable _could_ have been a problem with another compiler. Regardless – all […]