CNXSoft: This is a guest article by Dave Fohrn, Embedded Software Engineer at Cologne Chip AG, that goes into detail about the company’s open-source integrated logic analyzer (ILA) for GateMate FPGA chips. A field-programmable gate array (FPGA) is a highly flexible integrated circuit in which complex logic circuits can be configured. They are often used as custom computing units in digital circuits because of their ability to process data quickly and in parallel using individually configured circuits. The digital circuits designed specifically for FPGAs are usually developed in a hardware description language such as Verilog or VHDL and are known as gateware. The term “gate” refers to the configurable digital logic units in the FPGA on which the individual gate circuits are implemented. An effective design can accelerate the computing process by strategically utilizing the various resources available in the FPGA, processing data in parallel, and intelligent implementing pipelining. A […]

Cologne Chip releases an open-source integrated logic analyser (ILA) for GateMate FPGA chips

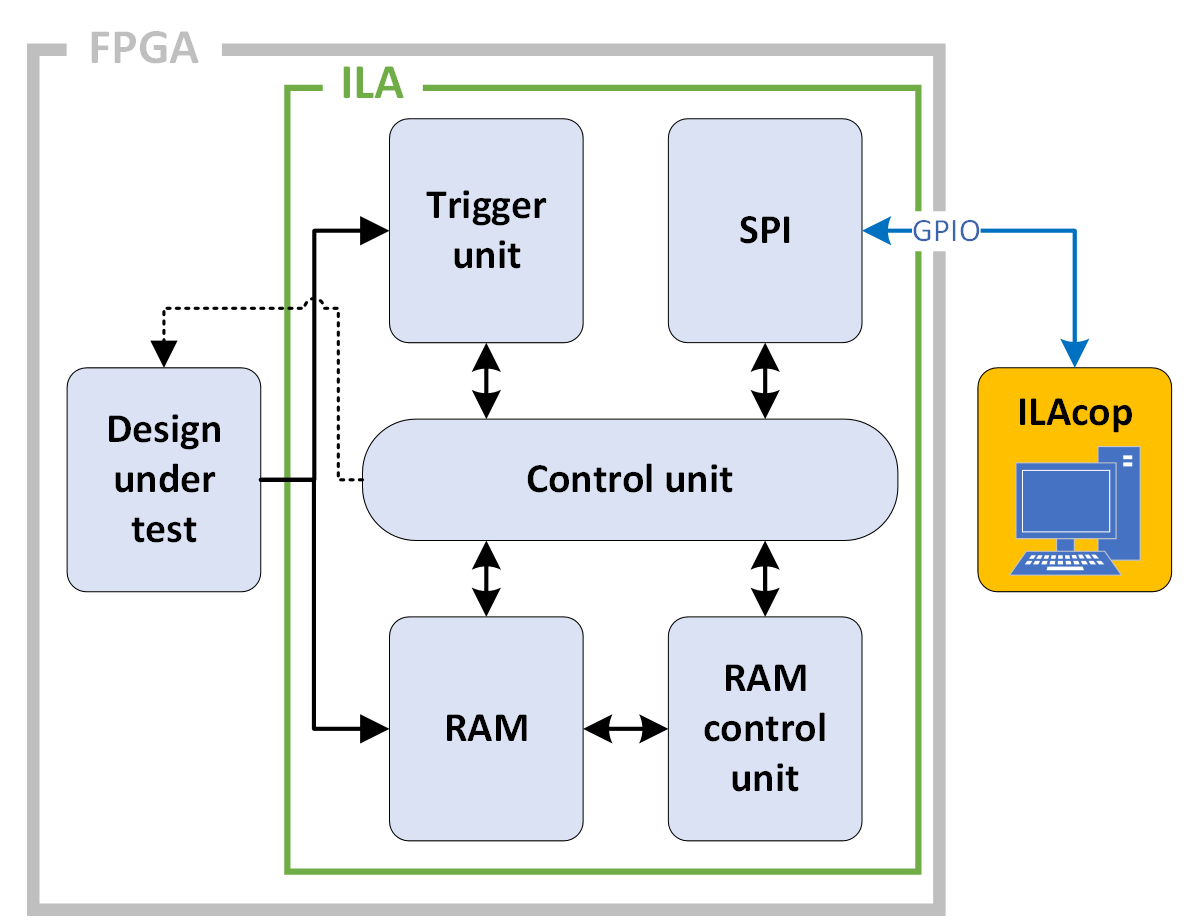

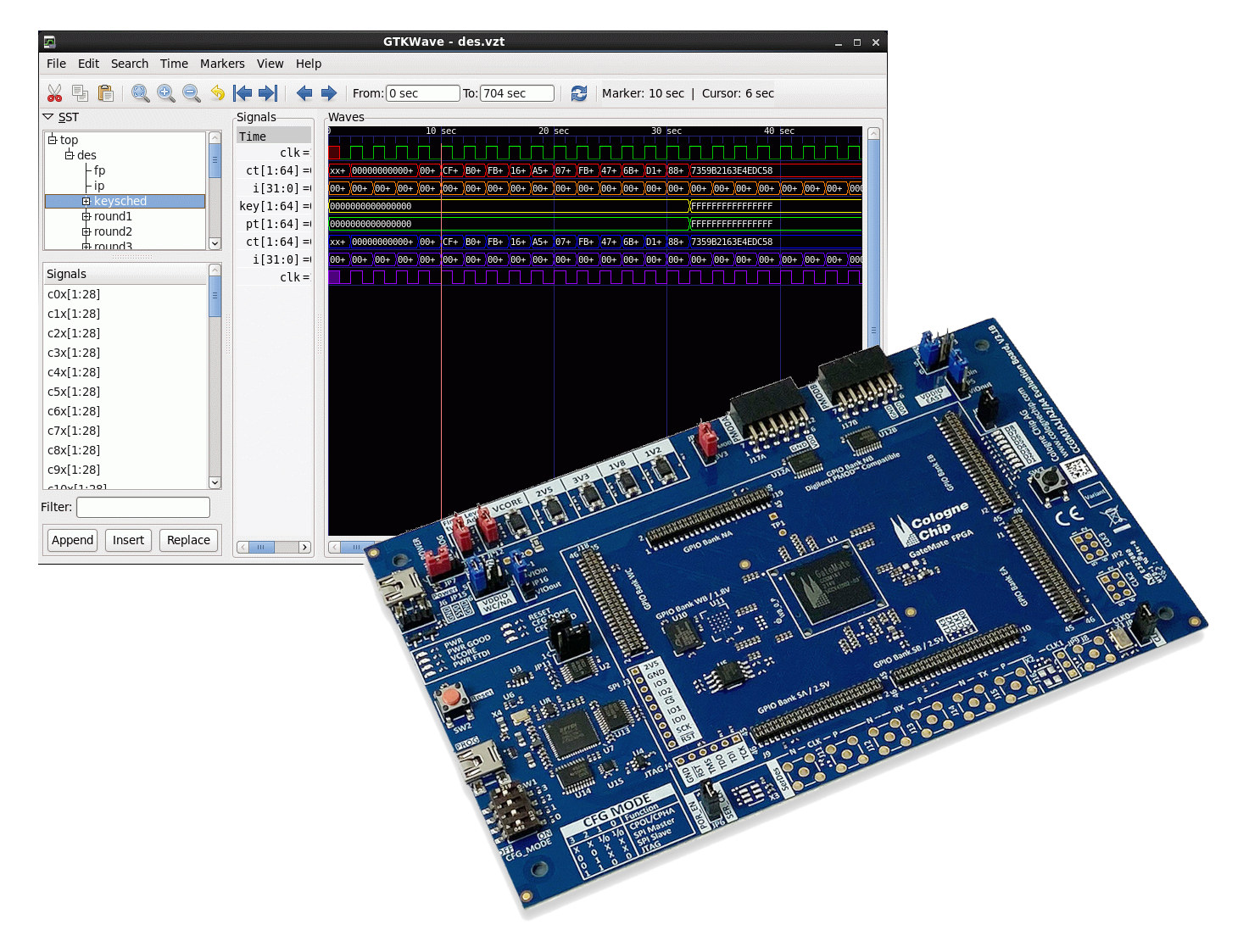

Cologne Chip’s “Integrated logic analyzer” (ILA) project is an open-source Verilog implementation of a logic analyzer running on the company’s GameMate A1 FPGA and designed to capture internal signals. When we first covered the GameMate A1 FPGA we noted Cologne relies on the open-source Yosys framework coupled with a proprietary, but free-of-charge, place & route tool contrary to most other FPGA vendors that only offer closed-source proprietary development tools. The German company has now released the GateMate integrated logic analyzer project to help customers debug their FPGA designs. The project includes the digital circuit of the ILA designed in the hardware description language Verilog and a Python program (ILA Control Program) used to configure the configuration of the ILA from the design under test (DUT) and provide an interface with the user during the debugging process. The user will also need a GateMate FPGA toolchain and GTKWave open-source program to […]

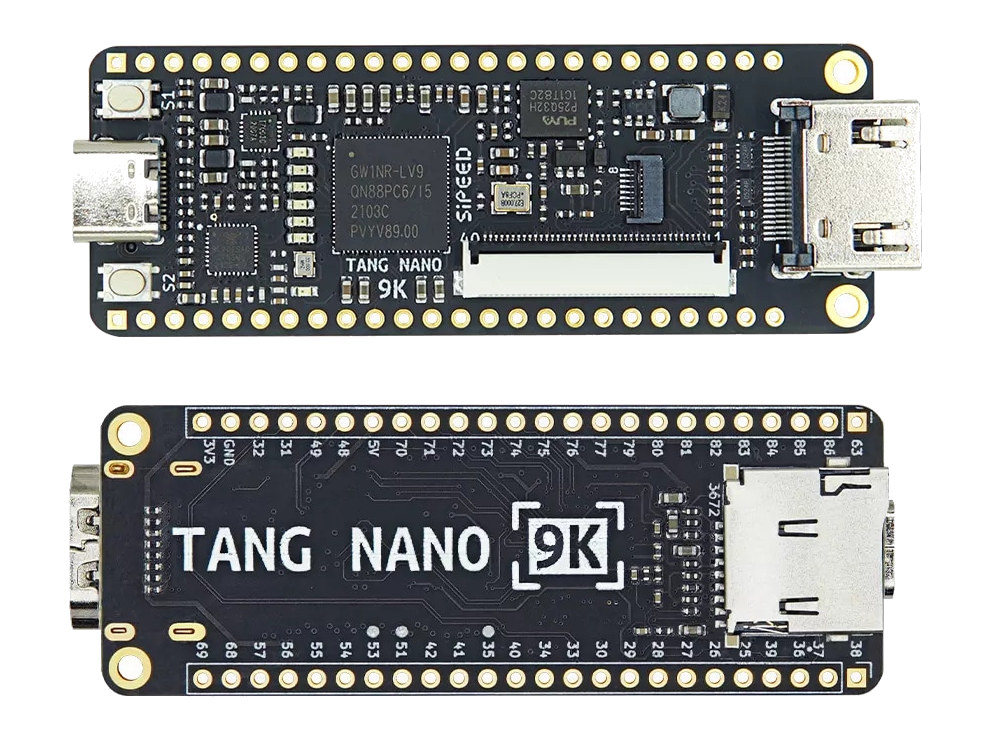

Tang Nano 9K FPGA board can emulate PicoRV32 RISC-V soft-core with all peripherals

Tang Nano 9K FPGA is the third board from Sipeed based on GOWIN FPGA following the original Tang Nano board with 1K LUT and Tang Nano 4K launched last year with GW1NSR-LV4C (aka GW1NSR-4C) FPGA offering 4068 logical units and 64 Mbit PSRAM, plus an Arm Cortex-M3 hard processor. As its name implies, the new board comes with 9K LUTs, as well as 64 Mbit PSRAM, 32 Mbit Flash, a micro SD card, and video I/O (HDMI, RGB LCD connector) that makes it suitable to run Verilog HDL code emulating a PicoRV32 RISC-V soft-core with all peripherals. Tang Nano 9K FPGA board specifications: FPGA – GOWIN LittleBee GW1NR-9/GW1NR-LV9 8,640 logical units (LUTs) 6,480 flip-flop 17,280 bits shadow SRAM (SSRAM) 486 Kbit block SRAM (BSRAM) 64 Mbit PSRAM 608 Kbit user flash 2x PLL Up to 276x user I/O Storage – 32 Mbit SPI flash. MicroSD card socket Display I/F HDMI […]

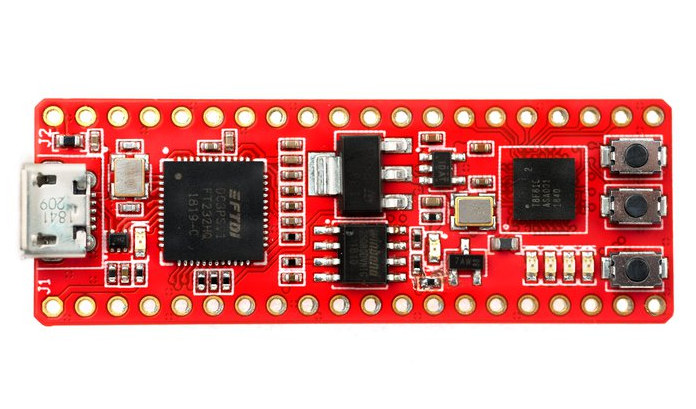

$30 FireAnt Development Board Features Efinix Trion T8 FPGA (Crowdfunding)

When I think FPGA, company names such as Xilinx, Altera (now Intel), or even Microsemi come to my mind. But there are also other companies such as Anlogic or Lattice Semi that offer FPGA chips. Today I’ve come across another FPGA silicon vendor, namely Efinix, with their Trion T8 FPGA found in XIPS Technology’s tiny FireAnt development board targeting makers and hardware designers. FireAnt specifications: FPGA – Efinix Trion T8 (T8F81C2) with 7384x LE counts, 8x embedded multipliers, 1x low-power oscillator, 1x PLL, 122.88 kbit internal RAM; Package – BGA-81 (5×5 mm) Storage – 8 Mbit serial NOR Flash Expansion – 2x 20-pin headers (soldered or unpopulated) with up to 35 GPIOs Debugging & Programming Micro USB 2.0 port via FTDI FT232HQ USB to serial chip JTAG signals in bottom layer Misc – Onboard 33.333 MHz crystal oscillator for PLL; 6x LEDs including 4 user configurable; 3x buttons (Reset, BTN1, […]

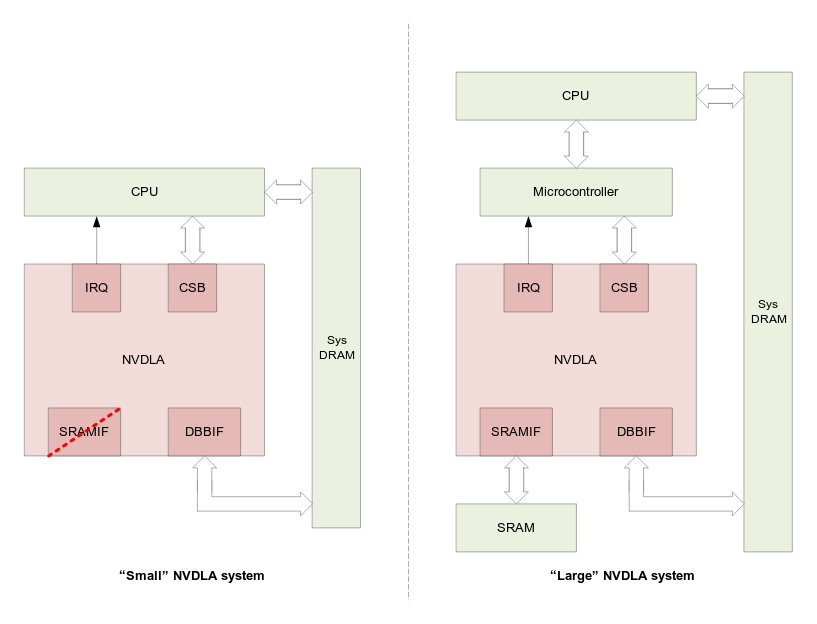

NVIDIA Unveils Open Source Hardware NVDLA Deep Learning Accelerator

NVIDIA is not exactly known for their commitment to open source projects, but to be fair things have improved since Linus Torvalds gave them the finger a few years ago, although they don’t seem to help much with Nouveau drivers, I’ve usually read positive feedback for Linux for their Nvidia Jetson boards. So this morning I was quite surprised to read the company had launched NVDLA (NVIDIA Deep Learning Accelerator), “free and open architecture that promotes a standard way to design deep learning inference accelerators” The project is based on Xavier hardware architecture designed for automotive products, is scalable from small to large systems, and is said to be a complete solution with Verilog and C-model for the chip, Linux drivers, test suites, kernel- and user-mode software, and software development tools all available on Github’s NVDLA account. The project is not released under a standard open source license like MIT, […]

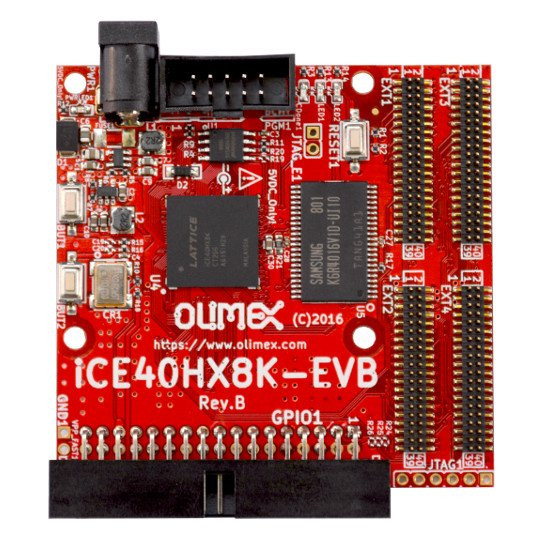

Olimex Introduces 40 Euros iCE40HX8K-EVB Board with Lattice ICE40 FPGA

Last year, Olimex launched their first FPGA board with iCE40HX1K-EVB. The board is very cheap at 22 Euros, but what you can do with it is limited since it only comes with 1280 logic cells. The company has now introduced an upgraded model called iCE40HX8K-EVB with 7680 logic cells, and more I/O headers. Olimex iCE40HX8K-EVB specifications: FPGA – Lattice Semi iCE40HX8K-CT256 FPGA with 7680 logic gates, 960 Logic Array Blocks, and 128 Kbit memory System Memory – 256Kx16 SRAM (512KB SRAM) Storage – 2MB serial flash Expansion 34-pin connector to access FPGA I/Os 4x 40 pin connectors for GPIOs Debugging / Programming – 10-pin “PGM” connector Misc – 2x user buttons, reset button, 2x user LEDs, power & programming status LEDs Power Supply – 5V via power jack Dimensions – 67×65 cm The board is open source hardware with the KiCAD schematics and PCB layout, BoM, and Gerber files available […]

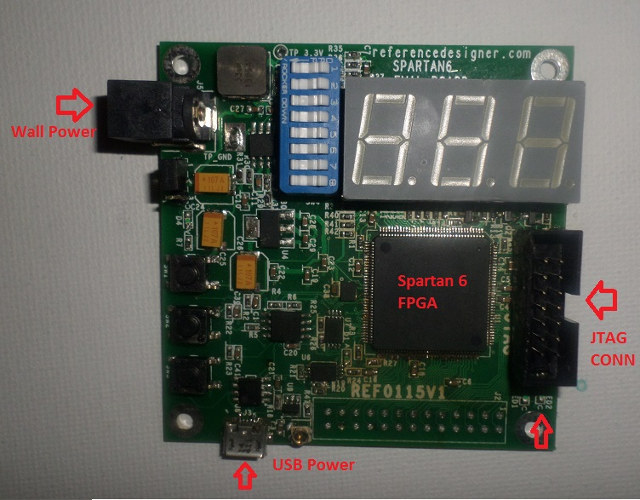

Spartixed is a $34 FPGA Board Based on Xilinx Spartan 6 (Crowdfunding)

Spartixed is another low cost FPGA board launched on Kickstarter, powered by Xilinx Spartan 6 LX4 FPGA, with a 7-segment display, some headers and buttons, and targeting people who want to learn VHDL/Verilog on the cheap. Spartixed board specifications: FPGA – Xilinx Spartan 6 LX4 FPGA (exact part not disclosed) Storage – 16 Mbit flash for program, I2C or SPI EEPROM Display – 3 digit 7- Segment Display USB – 1x micro USB port for power and debugging Expansion – 26-pin unpopulated header, optional SPI Bus A/D Converter Debugging – 14-pin JTAG connector, UARt port via USB connector Misc – 3x push button switches, 8 slide switches for input, 2x user LEDs, 1x power LED, 1x config. ready LED. Power – 5V via Micro USB Connector or 5 to 12 V via external power supply. Dimensions – N/A You can follow the project via its blog, and already access some […]