Before the BeagleBone and BeagleBone Black boards based on TI Sitara processor, there were BeagleBoard (-xM) boards powered by TI OMAP3 processors, and Beageboard.org and Texas Instruments are now working on their next open source hardware board with BeagleBoard-X15 powered by TI Sitara AM572 dual core Cortex A15 SoC.

Since Beagleboard-X15 has not been formally announced, there’s no picture, and we don’t have the full details yet, but here are the expect technical specifications:

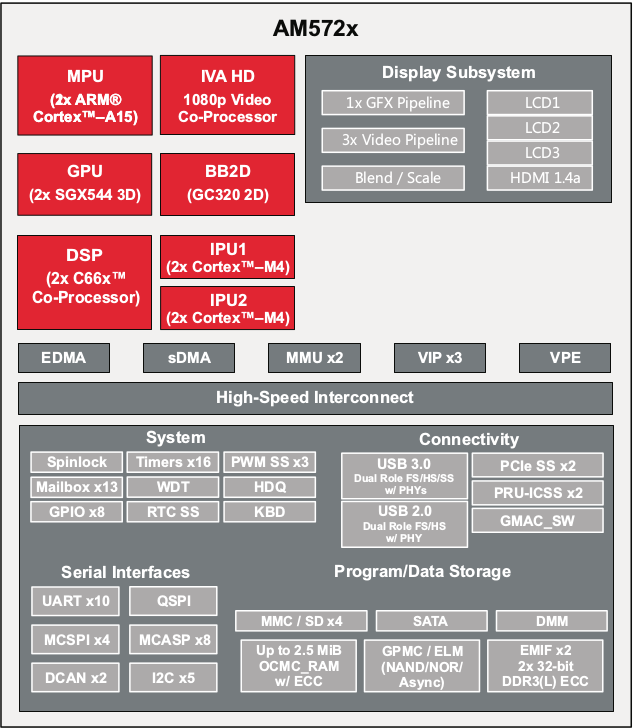

- SoC – Texas Instruments Sitara AM5728 dual core Cortex A15 processor @ 1.5 GHz, with PowerVR SGX544-MP2 3D GPU, Vivante GC320 2D GPU, 2x Cortex M4 cores, dual core C66x DSP, and IVA (Image and Video Accelerator) for 1080p video decode (H.264, VC-1, MPEG 1/2/4, AVS, etc..)

- System Memory – 2GB DDR3L with dual 32-bit buses

- Storage – 4GB eMMC, micro SD slot, and eSATA interface

- Video I/O – HDMI out up to 1080p60, LCD port, and Video IN

- Audio I/O – HDMI out, analog audio In/Out

- Connectivity – 2x Gigabit Ethernet ports

- USB – 3x USB 3.0 ports

More details will eventually show up on BeagleBoard-X15 Wiki (currently empty), in the meantime you can always check the boot log. Pricing and availability info are not available either, but the board will hopefully start selling in Q1 2015, or Q2 at the latest. is scheduled to launch in late February of 2015.

Texas Instruments has not formally announced their AM5x processor, but you can already get all details about AM5728 and AM5726 processors (codenamed J6/Vayu”), since the company has published a 7,229 pages “AM572x ARM Processor Technical Reference Manual“. There’s also a single core Cortex A15 processor family called AM571x “J6Eco” that should become available this quarter with AM5716 and AM5718.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress. We also use affiliate links in articles to earn commissions if you make a purchase after clicking on those links.

ah ah ! I first posted the boot log for the joke but it seems that it is interesting for the curious among us! 🙂

Both of those Interrupt Processing Units have two Cortex-M4 cores, so 2 * 2 = quad cores for interrupt offloading, mmm, yammy for realtime processing… Pretty much perfect for GPIO/CNC… Even OpenCV might run nicely in combo with those Cortex-A15 processors.

DIMM slots for user expandable RAM?

A proper SATA power connector, or a power jack? NOT a usb power connector, please…

@Alan

The picture is up on the wiki.

Soldered RAM, and the SATA connector is not soldered, but it should be on the left side of the pic.

@cnxsoft

‘e-sata’ is between the dual ethernet stack and hdmi on the far side

More like panda board 2

just like omap5 serial chip!amazing .I guess the board will be welcome!

@anon

IPU actually stands for Image Processing Unit (just an fyi) 🙂

I’ve never actually heard of dedicated Interrupt chips, those are usually build in with the various subsystems.

built*

Very very interesting. I will have to dig into this as this guy should have enough power to do a very very credible CNC controller. It looks like you have the hardware to run Linux, CNC controller and a PLC controller all on this one board.

@bnmguy

Whoops, recalled different arch, too bad everyone naming their stuff with the same silly acronyms, still some people thinking using acronyms is somehow “cool”, instead of using as generic English names as possible. 🙂

I’m a bit hesitant to buy BeagleBoard, especially if it contains another TI OMAP chip. On the BeagleBone Black, they still don’t have a completely working OpenGL ES layer (and SDL 2). Yeah, you can possibly cobble it together, but I can get it out of the box on almost any other board. It sounds like they’ll continue to be at the mercy of TI to update the driver.

It looks like the Dual ethernet ports are nothing more than a single MAC split via an on-chip switch. That is quite a disappointment.

From the manual:

“One 3-port Gigabit Ethernet Switch subsystem (10, 100, or 1000 Mbps). The switch provides two

external Ethernet ports and one internal CPPI interface port with AVB/Industrial Ethernet and 802.1ae

support. Included support for 3.3-V RMII/MII and 1.8- or 3.3-V RGMII.”

@Thad

I’ve done extensive work with the ethernet subsystems in this chip (as they were implemented in earlier chips) and unless the 3PSW module has changed significantly, it can be used as a switch (which enables you to daisy-chain a bunch of these together, as there’s an internal DMA-based interface to the switch as well as the two external ports) or as two separate interfaces. When using it as a switch, you can program the forwarding table to control the forwarding behavior based on MAC address and VLAN. It’s really rather cool.

This is actually mostly the same ethernet hardware that’s in the BBB, it’s just that both PHYs are populated on this board. It looks as if the IPUs are a sort of replacement for the BBB’s PRUs (though perhaps there are undocumented PRUs here as well), and although they will not be as deterministic in execution as the PRUs were, they should be FAR more powerful and therefore capable of doing most of the same tasks via effective programming of the IPU interrupts. This should be *excellent* for anyone implementing real-time tasks, as M4s have a completely C-programmable interface rather than an obscure custom assembly language.

The “AVB support” noted in the description is actually really cool; AVB is a collection of IEEE standards that provide *guaranteed bandwidth and latency limits* across Ethernet links and precise time synchronization (sub-microsecond synch of “wall clock” time) which is useful for audio/video applications as well as industrial control. The next-generation of AVB (now renamed to TSN, for Time-Sensitive Networking) is in progress in the IEEE and is eagerly anticipated by both automotive and industrial automation markets. There’s likely a lot of software work left to fully get the AVB protocols working (I designed and implemented an AVB stack for a similar TI processor) but it’s very cool stuff regardless.

@Levi

If you check the TRM you’ll see it actually has two PRU-ICSS instances (each with two PRU cores) _and_ two IPU instances (each with two Cortex-M4 cores). Vayu is really an insane chip, they seem to have crammed almost every major subsystem found on a recent TI SoC onto one die (and typically more than one instance of each).

IPU, also known under the codename “Benelli”, is actually an evolution of the “Ducati” dual cortex-M3 subsystem found in the OMAP4 and TI81xx (Netra and Centaurus) processors (called “Media Controller” in the latter). They’re basically designed for micro-managing video-related peripherals without burdening the main CPU with frequent but easily handled tasks. On processors which have an ISS instance (OMAP4 and Centaurus) Ducati is clocked synchronously to it and has a dedicated port to the ISS configuration interconnect, completely bypassing the L3, to give it very low latency access. If you’ve ever had a smartphone crash with the camera active and happily continuing to show the camera image (complete with auto-focus/exposure etc) even though the main CPU died, it’s this sort of arrangement that’s responsible.

@Matthijs van Duin

“frequent but easily handled tasks”, forgot to include the most important aspect: hard real-time.

Note that the OMAP543x also has an ISS instance (fancier than the one in the OMAP4), coupled to its IPU instance. See its TRM for block diagrams of that arrangement.

I’d also add that the PRUs are specifically meant to implement EtherCAT and all sorts of weird (mostly industrial) bus protocols, invariably relying on the PRU’s trivial instruction timing to create the protocol’s timing. Use of a compiler of any sort therefore kind of defeats their purpose, although a C compiler is available nonetheless. IPU would be completely useless as a replacement for these kinds of applications.