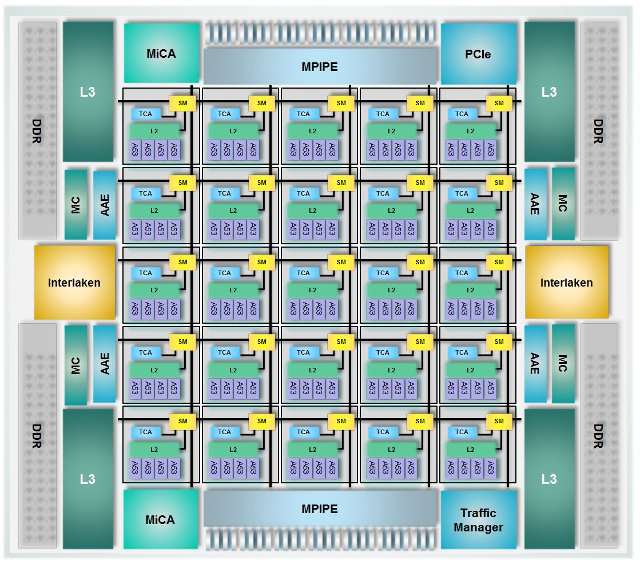

As ARM gets into the server and networking business, the number of ARM cores in SoC starts to shoot up, and after Cavium ThunderX 48 core processor, here comes EZChip TILE-Mx100 Hecta-core network processor with 100 ARM Cortex A53 cores and capable of delivering up to 200 Gigabit throughput.

Key features listed for EZchip TILE-Mx100:

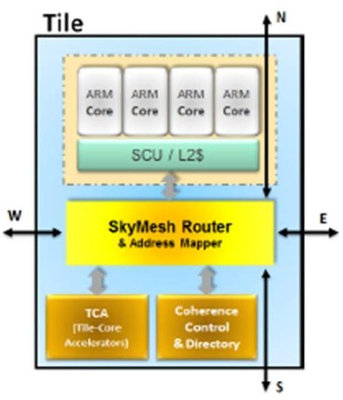

- One hundred 64-bit ARM Cortex A53 CPU cores in one chip

- 3-level coherent cache architecture with over 40 Mbytes on-chip cache.

- DDR4 DRAM controllers with ECC and supporting up to 1TBytes of memory.

- SkyMesh coherent architecture for massive bandwidth, low latency and linear scalability

- Multitude of networking hardware accelerators for high-performance data-path packet processing including

- Wire-speed mPIPE packet processing engine delivering 300 million packets-per-second I/O.

- Integrated 5-level hierarchical Traffic Manager with 256,000 queues.

- MiCA™ acceleration engines for over 100Gbps of crypto.

- Over 200Gbps of integrated I/O including 1G, 10G, 25G, 40G, 50G, 100G Ethernet, Interlaken, PCIe 3.0.

- Precision packet timestamp and IEEE1588v2 support.

- Best power/performance ratio for small systems’ rack and power footprint

Target networking applications for the processor include load balancing, security, network monitoring, NFV & SDN, virtualization, IDS/IPS (Intrusion Detection/Prevention), application recognition and video processing, for markets such as data center, cloud, enterprise and carrier networks. The processor will also leverage ARM software and tools, run Linux, and supports C/C++ / Java programming model, as well as hypervisors like KVM or Xen.

TILE-Mx is scheduled to sample in the second half of 2016, and the company also plans to offer 64 and 36 ARM cores version of the chip. More details can be found on EZchip TILE-Mx Multicore processor page, and a presentation will be given at the Linley Data Center Conference on February 25, 2015 in San Jose, California.

Via EETimes.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

Oh yeah… A NoC… These would go great as the backbone number crushers behind the systems used for human-machine interface (or was it “human-man interface”, actually the original is “man-machine interface”), an library/main computer to the desktops. (LCARS, heh)

And those Interlaken ports is a tad more open way of doing it, rather than “open” FreedomFabric, and its cousins.

Perfect tool for those cold lonely nights at the NSA data interception node.

Back to the future -> bit like an Inmos Transputer except few more cores and no funky special language to use.

Sounds like they’re aiming at the fpgas used in some mobile base stations

Recent video about Tile MX-100 at Linaro Connect SFO 2015

https://www.youtube.com/watch?t=12&v=EioJOOd-a3U