SiFive has just announced the availability of their new E2 Core IP Series low-area, low-power microcontroller cores designed for use in embedded devices. Two standards cores are currently part of the new family:

- E21 providing mainstream performance for MCUs, sensor fusion, minion cores and smart IoT markets

- E20, the most power-efficient SiFive standard core designed for microcontrollers, IoT, analog mixed signal and finite state machine applications

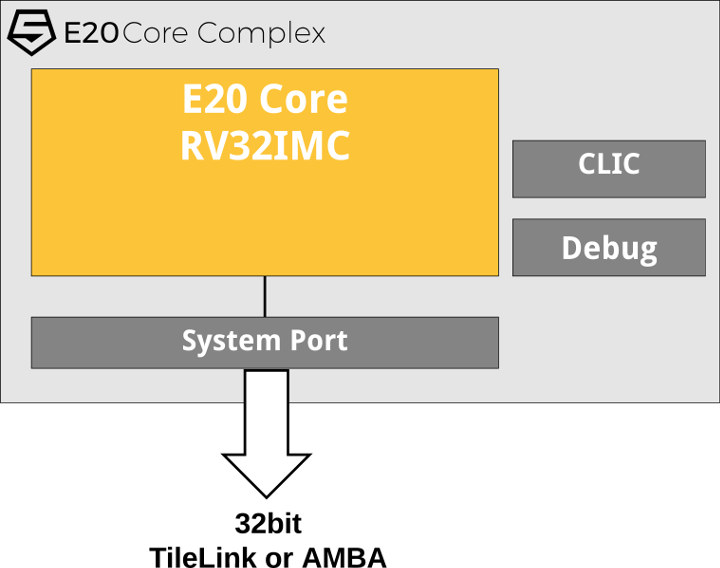

SiFive E20 MCU Core

SiFive E20 Standard Core IP Key Features:

- RISC-V ISA – RV32IMC

- Machine Mode only

- 2-stage pipeline

- System Port for external memory accesses

- Core Local Interrupt Controller (CLIC) with 32 interrupts

- Advanced debug with 4 hardware breakpoints/watchpoints

- Performance – 1.1 DMIPS/MHz; 2.4 CoreMark/MHz

- Power / Clock / Area

- 28nm HPC – 0.58 mW; 725 MHz and up; 0.023 mm2

- 55nm LP – 1.3 mW; 250 MHz and up; 0.064 mm2

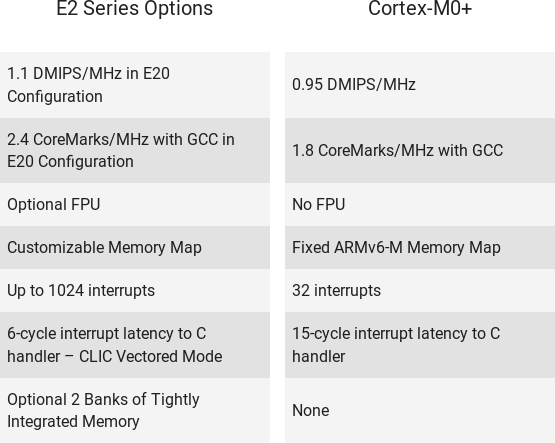

The company compares E20 core to Arm Cortex-M0+ core in the table below.

Everything is favorable to E20 core in that table, but it may be worth mentioned power consumption comparison is missing, although E20 can do more work per MHz. Arm’s Cortex M0+ page mentions the “Cortex-M0+ achieves a power consumption below 4µW/MHz (40LP process, base configuration), while reaching a performance of 2.46 CoreMark/MHz”, which differs from the number provided in the table, although SiFive reports the test was done with GCC, so not just a theoretical number.

Everything is favorable to E20 core in that table, but it may be worth mentioned power consumption comparison is missing, although E20 can do more work per MHz. Arm’s Cortex M0+ page mentions the “Cortex-M0+ achieves a power consumption below 4µW/MHz (40LP process, base configuration), while reaching a performance of 2.46 CoreMark/MHz”, which differs from the number provided in the table, although SiFive reports the test was done with GCC, so not just a theoretical number.

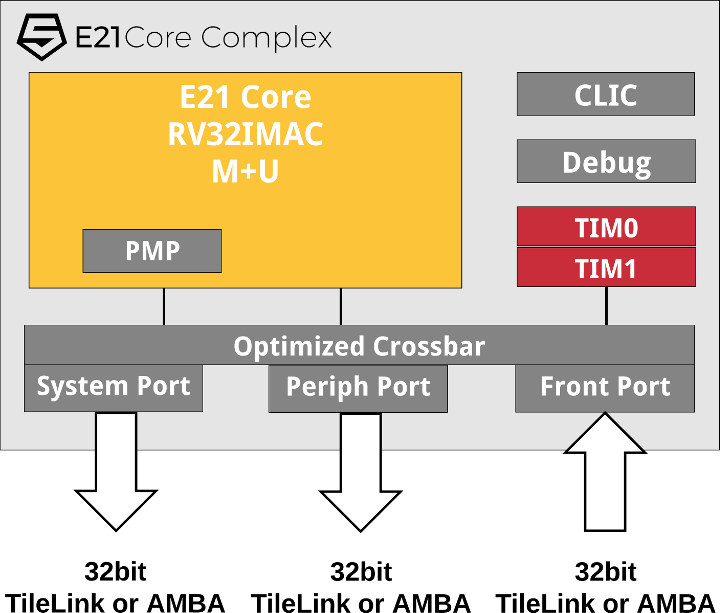

SiFive E21 MCU Core

SiFive E21 Standard Core IP Key Features:

- RISC-V ISA – RV32IMAC

- Machine and User Mode with 4 Region Physical Memory Protection

- 3-stage pipeline with Simultaneous Instruction and Data Access

- 2 Banks of Tightly Integrated Memory

- System, Peripheral, and Front Ports

- CLIC interrupt controller with 127 interrupts

- Advanced debug with 4 hardware breakpoints/watchpoints

- Performance – 1.38 DMIPS/MHz; 3.1 CoreMark/MHz

- Power / Clock / Area

- 28nm HPC – 1.3 mW; 585 MHz and up; 0.037 mm2

- 55nm LP – 3.1 mW; 210 MHz and up; 0.1 mm2

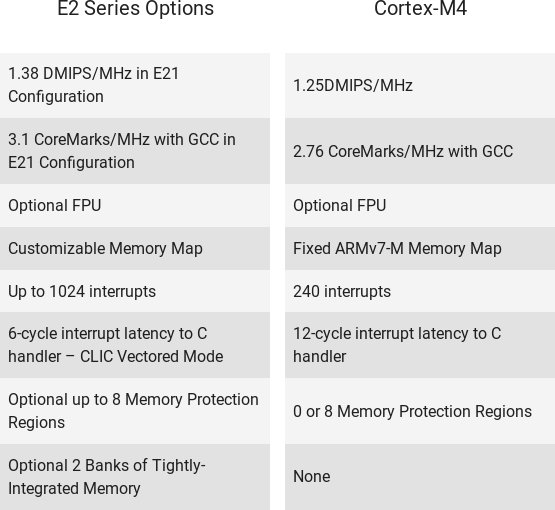

SiFive E21 core is compared to Cortex M4 core.

The same disclaimer applies to this table.

The same disclaimer applies to this table.

SiFive provides both RISC-V Core IP in Verilog, a test bench, a software development kit, as well as a user guide dealing with integration, synthesis & constraints, and the test bench.

You’ll find more details on SiFive E2 series page, where you can also download the FPGA bitstream for Artix-7 based Digilent Arty A7-35T evaluation kit, and/or request for the evaluation RTL.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

Regarding: | “Cortex-M0+ achieves a power consumption below 4µW/MHz (40LP process, base configuration), while reaching a performance of 2.46 CoreMark/MHz”, which differs from the number provided in the table, although SiFive reports the test was done with GCC, so not just a theoretical number. | Vendors using Arm CM cores tend to build coremark with IAR, which yields superior performing code compared to GCC. The 2.46 CoreMark/MHz is valid (and in-fact is a bit dated, current scores are a bit higher). Perhaps SiFive should consider building CoreMark for RV32I with IAR as well, and then the comparison would… Read more »