FOSDEM 2020 will take place next week, and there will be several interesting talks about open-source hardware and software development. One of those is entitled “Open ESP – The Heterogeneous Open-Source Platform for Developing RISC-V Systems” with an excerpt of the abstract reading:

ESP is an open-source research platform for RISC-V systems-on-chip that integrates many hardware accelerators.

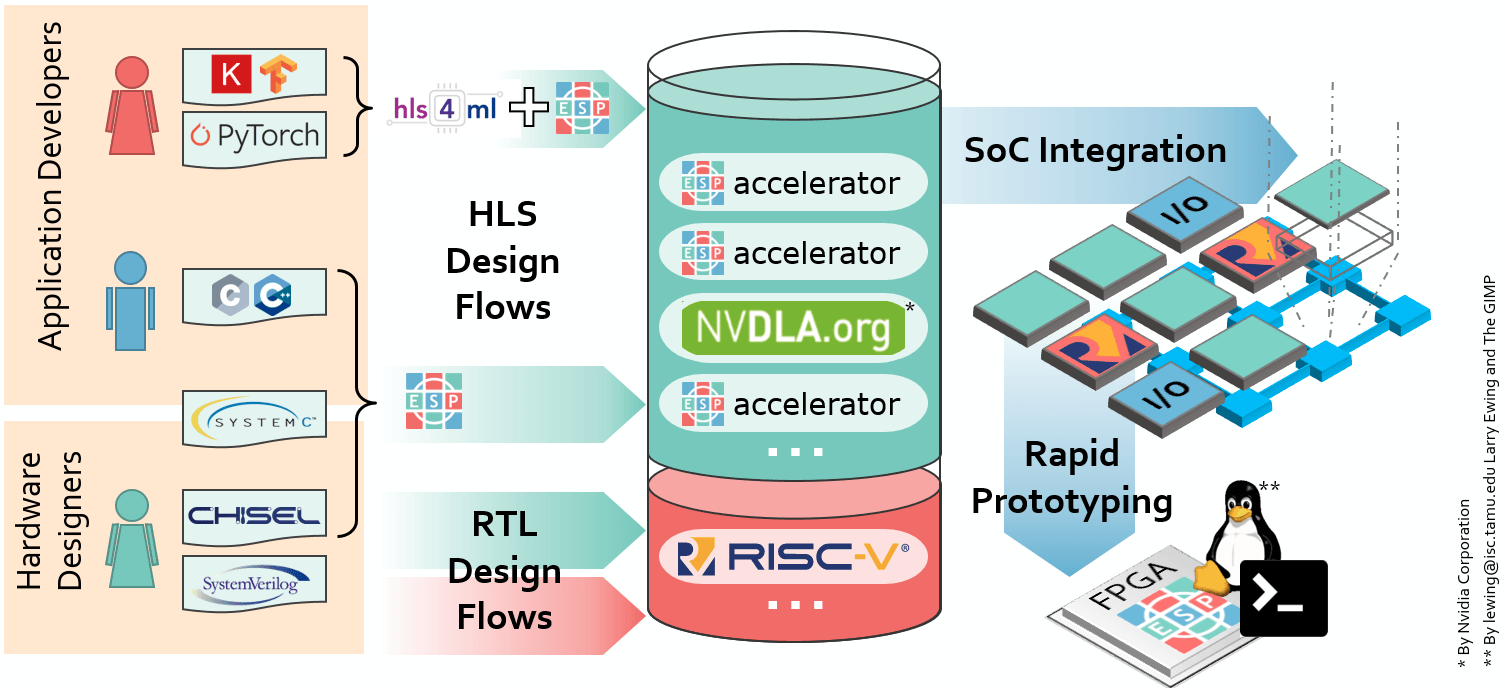

ESP provides a vertically integrated design flow from software development and hardware integration to full-system prototyping on FPGA. For application developers, it offers domain-specific automated solutions to synthesize new accelerators for their software and map it onto the heterogeneous SoC architecture. For hardware engineers, it offers automated solutions to integrate their accelerator designs into the complete SoC.

If we go to the official website, we can see ESP (Embedded Scalable Platform) actually supports both 32-bit Leon3 (Sparc) and 64-bit Ariane (RISC-V) cores, and various hardware accelerators from the platform or third parties.

Highlights:

- Architecture

- Accelerators

- ESP accelerators

- Cadence Stratus HLS flow

- Xilinx Vivado HLS flow

- Chisel flow

- Third-Party Accelerators – NVIDIA Deep Learning Accelerator (NVDLA)

- ESP accelerators

- Design Flows

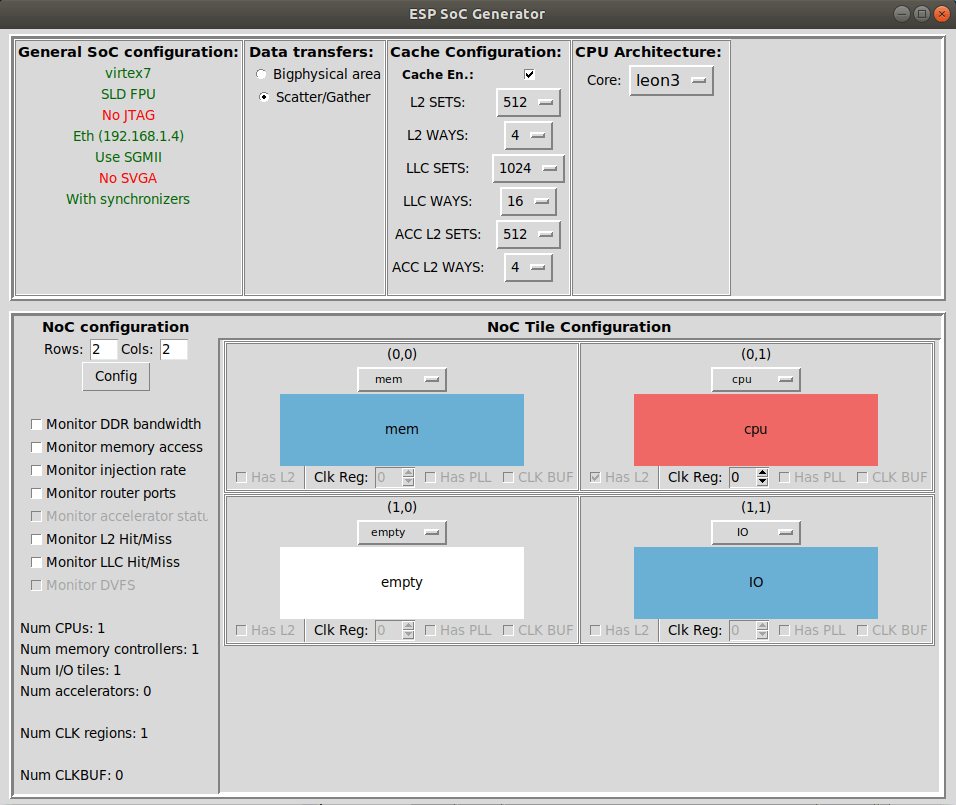

ESP is compatible with FPGA development boards such as Xilinx Virtex UltraScale+ FPGA VCU118, Xilinx Virtex-7 FPGA VC707, or proFPGA quad Virtex7 prototyping system, which in turn can run Linux SMP on the RISC-V or Sparc cores.

ESP was initially designed to run on CentOS 7 and is still the recommended OS, but Ubuntu 18.04 support has recently been added. Required components include various packages from the OS (Python, Perl, Qt, etc..), commercial tools from Cadence, Xilinx, and/or Mentors Graphics, as well as RISC-V and/or Sparc toolchains.

You can follow the tutorials for installing ESP on Centos or Ubuntu, and create your first single-core or multi-core SoC with ESP SoC Generator user interface as explained in the documentation.

More tutorials are planned especially focused on the design of accelerators. If you’d like a more in-depth overview of the Embedded Scalable Platform, you may want to watch that 16-minute video published a few weeks ago.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress. We also use affiliate links in articles to earn commissions if you make a purchase after clicking on those links.

Nice tool. The only downside is: it depends on Cadence and Mentor Graphics. It may be worth thinking about open source tools … example: https://theopenroadproject.org/ (RTL to GDS, currently apha)

Nice TCL/TK GUI! Brings me memories from back in the days where I was doing perl+tcltk 🙂

> Open source research platform

> Required components include … commercial tools from Cadence, Xilinx and Mentor Graphics

So the open source platform (at the “Free and Open Source” conference no less) requires commercial closed source tools? huh?

The platform is open source. The embedded tools are not. There are relative easy ways to change this. I mentioned one open source toolchain. You may get the required open source tools from there. This way the open source platform becomes an open source developmet system.