Linux 6.2 has just been released with Linus Torvalds making the announcement on LKML as usual: So here we are, right on (the extended) schedule, with 6.2 out. Nothing unexpected happened last week, with just a random selection of small fixes spread all over, with nothing really standing out. The shortlog is tiny and appended below, you can scroll through it if you’re bored. Wed have a couple of small things that Thorsten was tracking on the regression side, but I wasn’t going to apply any last-minute patches that weren’t actively pushed by maintainers, so they will have to show up for stable. Nothing seemed even remotely worth trying to delay things for. And this obviously means that the 6.3 merge window will open tomorrow, and I already have 30+ pull requests queued up, which I really appreciate. I like how people have started to take the whole “ready for […]

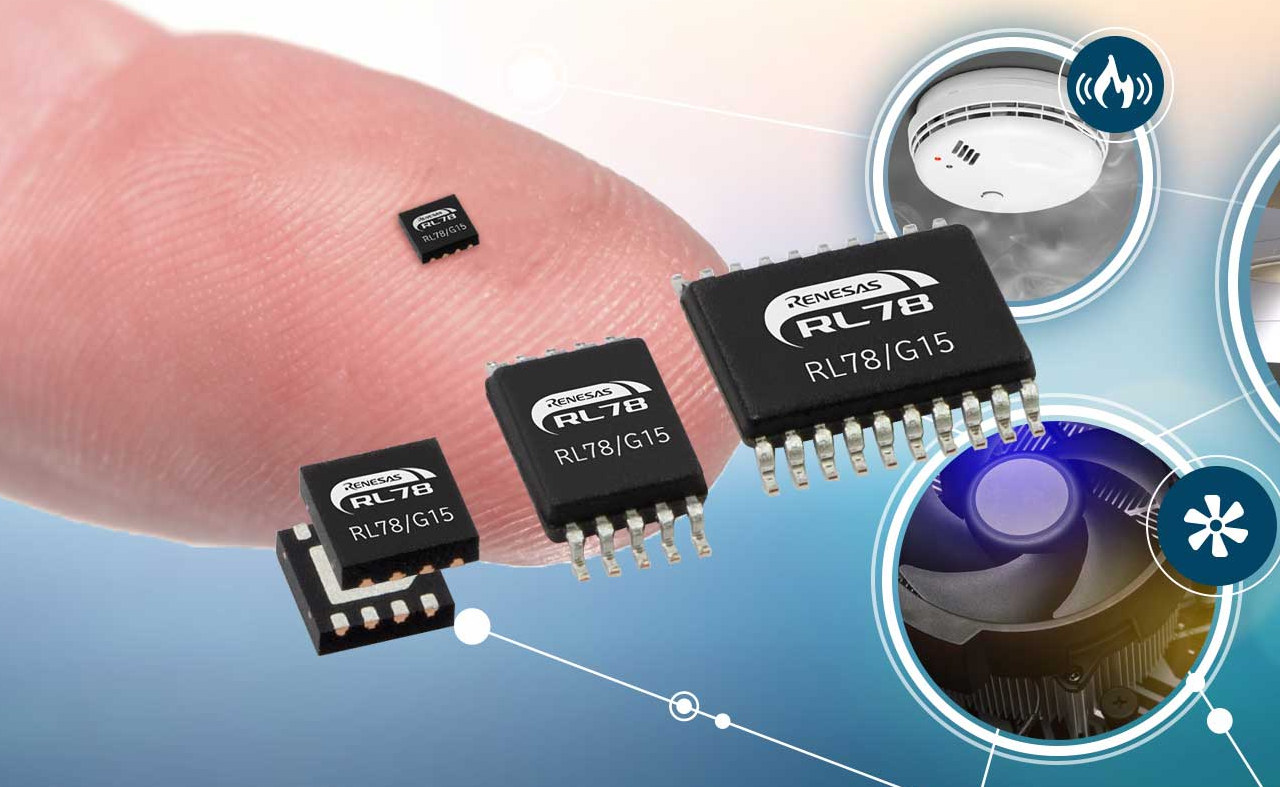

Renesas RL78/G15 8-bit MCU is offered in a 3x3mm package

Renesas Electronics RL78/G15 is an entry-level 8-bit microcontroller with 1 KB of SRAM, 4 or 8KB of code flash memory, and offered in package sizes ranging from 8 to 20 pins, down to an 8-pin device measuring just 3×3 mm. STMicro has just unveiled the STM32C0 32-bit microcontroller claiming “your next 8-bit MCU is a 32-bit” with packages from 8- to 48-pins and packages as small as 1.70 x 1.42 mm and 3x3mm, and a price similar to other 8-bit industrial microcontrollers. To that, I say “not so fast STMicro!”, as Renesas has just launched the 16 MHz RL78/G15 8-bit microcontroller family with many of the same features and target use cases as the STMC32C011 sub-family. Renesas RL78/G15 key features and specifications: CPU core – Renesas RL78 8-bit core @ up to 16 MHz Memory – 1NS SRAM, Storage – 4 to 8KB program flash, 1KB data flash Peripheral I/F […]

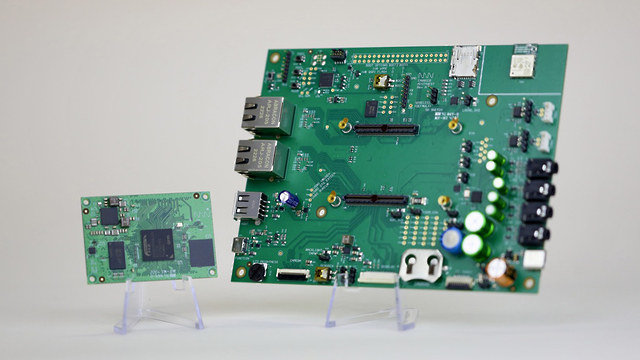

MistySoM Renesas RZ/G2L or RZ/V2L SoM and devkit goes for $112 and up

We’ve previously written about several system-on-modules and SBCs based on Renesas RZ/G2L or RZ/V2L Cortex-A55/M33 processors such as Geniatech “AHAURA” RS-G2L100 and “AKITIO” RS-V2L100 single board computers, Forlinx FET-G2LD-C system-on-module, and SolidRun RZ/G2LC SOM and devkit. But most of those are hard to buy, and you need to contact the company, discuss your project, etc… before purchase, except for the SolidRun Renesas RZ/G2LC Evaluation Kit going for $249. Another option is the MistyWest MistySOM module offered for $112 and up on GroupGets with either Renesas RZ/G2L or RZ/V2L processor, as well as an optional carrier board. MistySOM system-on-module MistySOM-G2L (aka MW-G2L) and MistySOM-V2L (aka MW-V2L) specifications: SoC – Renesas RZ/G2L or RZ/V2L with dual-core Cortex-A55 processor @ 1.2 GHz, Arm Cortex-M33 core @ up to 200 MHz, Arm Mali-G31 GPU, and DRP-AI vision accelerator (RZ/V2L only) System Memory – 2GB LPDDR4/DDR4 Storage – 32GB eMMC flash 2x 120-pin high-speed mezzanine […]

Linux 6.1 LTS release – Main changes, Arm, RISC-V and MIPS architectures

Linus Torvalds announced the release of Linux 6.1, likely to be an LTS kernel, last Sunday: So here we are, a week late, but last week was nice and slow, and I’m much happier about the state of 6.1 than I was a couple of weeks ago when things didn’t seem to be slowing down. Of course, that means that now we have the merge window from hell, just before the holidays, with me having some pre-holiday travel coming up too. So while delaying things for a week was the right thing to do, it does make the timing for the 6.2 merge window awkward. That said, I’m happy to report that people seem to have taken that to heart, and I already have two dozen pull requests pending for tomorrow in my inbox. And hopefully I’ll get another batch overnight, so that I can try to really get as […]

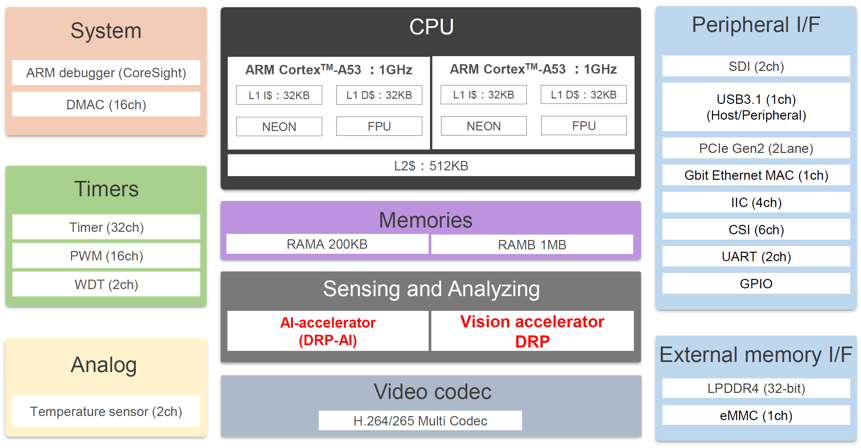

Renesas RZ/V2MA microprocessor embeds AI & OpenCV accelerators for image processing

Renesas has launched the RZ/V2MA dual-core Arm Cortex-A53 microprocessor with a low-power (1TOPS/W) DRP-AI accelerator and one OpenCV accelerator for rule-based image processing enabling vision AI applications. The MPU also supports H.265 and H.264 video decoding and encoding, offers LPDDR4 memory and eMMC flash interfaces, as well as Gigabit Ethernet, a USB 3.1 interface, PCIe Gen 2, and more. The RZ/V2MA microprocessor targets applications ranging from AI-equipped gateways to video servers, security gates, POS terminals, and robotic arms. Renesas RZ/V2MA specifications: CPU – 2x Arm Cortex-A53 up to 1.0GHz Memory – 32-bit LPDDR4-3200 Storage – 1x eMMC 4.5.1 flash interface Vision and Artificial Intelligence accelerator DRP-AI at 1.0 TOPS/W class OpenCV Accelerator (DRP) Video H.265/H.264 Multi Codec Encoding: h.265 up to 2160p, h.264 up to 1080p Decoding: h.265 up to 2160p, h.264 up to 1080p Networking – 1x Gigabit Ethernet USB – 1x USB 3.1 Gen1 host/peripheral up to 5 […]

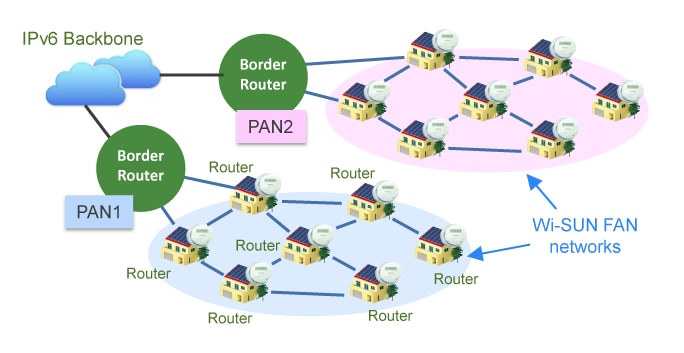

Wi-SUN: An LPWAN standard for Smart Cities, Smart Agriculture, large scale IoT deployments

Wi-SUN is a standard (IEEE 802.15.4g) managed by the Wi-SUN Alliance and designed for Smart Cities, Smart Agriculture, and other large scale IoT deployments with a large number of devices thanks to the use of IPv6 mesh networking. The organization was founded in 2011 to “support the worldwide development of Wireless Communications Networks for Utilities, Smart Cities and IoT”, but due to the niche nature of target applications, it does not get that much press coverage and was only recently brought to my attention. Wi-SUN stands for “Wireless Smart Utility Networks”or “Wireless Smart Ubiquitous Networks”, and the standard aims to connect streetlights, cameras, weather stations, smart metering, utility transmission systems, and others to enable data-sharing between city services to improve their efficiency, save costs, and offer improves services to citizens. Wi-SUN FAN (Field Area Network) is the latest protocol managed by the Wi-SUN Alliance with over 95 million units shipped […]

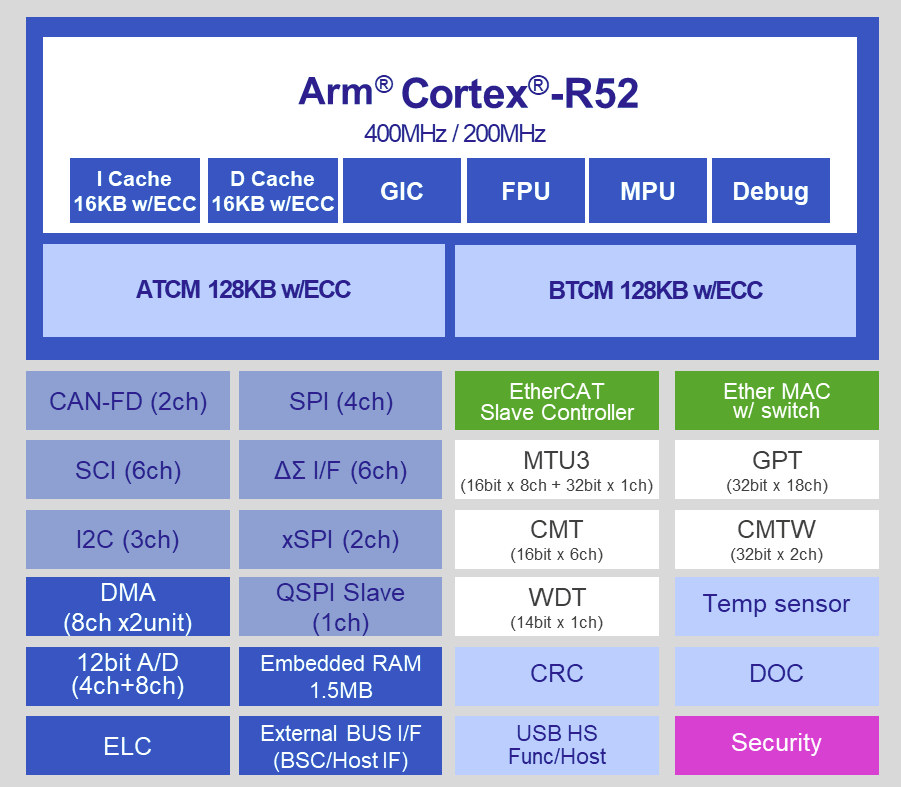

Renesas RZ/N2L Arm Cortex-R52 MPU targets industrial Ethernet and TSN

Renesas RZ/N2L is an Arm Cortex-R52 microprocessor (MPU) family for industrial Ethernet communication equipped with an integrated TSN-compliant 3-port Gigabit Ethernet switch and an EtherCAT slave controller. The new processors also support other major industrial network communication protocols such as EtherCAT, PROFINET RT, EtherNet/IP, and OPC UA, as well as the new PROFINET IRT (Isochronous real-time) that allows deterministic communication with cycle times down to 31.25 µs and one µs of jitter. Renesas RZ/N2L key features and specifications: CPU – Arm Cortex-R52 @ up to 400MHz with 16KB I-cache with ECC, 16KB D-cache with ECC Memory Tightly coupled memory – 256KB with ECC Internal RAM – 1.5MB with ECC Octa/Quad SPI for HyperRAM, HyperFLASH, SRAM, SDRAM Networking Ethernet L2 switch: 3x external ports with Gigabit support TSN support (IEEE 802.1AS-2020, IEEE 802.1Qbv/802.3br, IEEE 802.1Qbu, etc.) Network redundancy support (DLR, PRP) EtherCAT slave controller Industrial Ethernet – EtherCAT, PROFINET RT/IRT, EtherNet/IP, […]

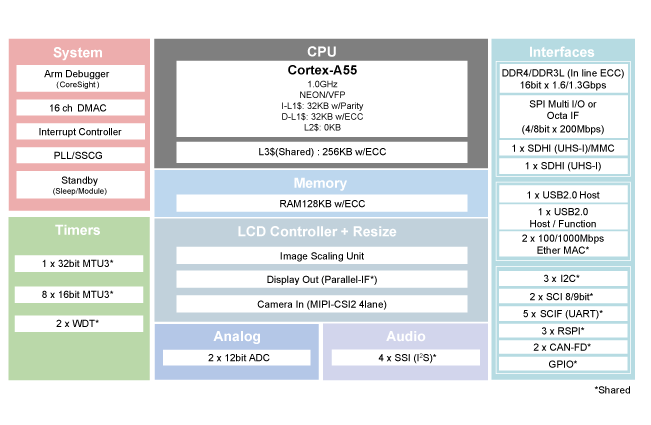

Renesas RZ/A3UL Cortex-A55 CPU runs RTOS for HMI with quick startup times

Renesas RZ/A3UL is a single-core Cortex-A55 processor clocked at up to 1 GHz designed to run FreeRTOS or Azure RTOS on high-definition (1280×800) HMI solutions requiring quick startup times such as industrial equipment, home appliances, office automation equipment, audio equipment, and POS terminals. The new RZ/A3UL processor family has the same peripheral functions and package pin assignments as the RZ/G2UL (Arm Cortex-A55/M33) and RZ/Five (RISC-V) families targeting Linux-based HMI applications. Renesas also designed a SMARC 2.1 compliant System-on-Module (SoM) based on the Renesas RZ/A3UL microprocessor to speed up time to market. Renesas RS/A3UL specifications: CPU – Single-core Arm Cortex-A55 processor @ up to 1.0 GHz with 32KB I-cache with parity, 32KB D-cache with ECC, 256KB L3 cache with ECC Internal Memory – 128KB SRAM with ECC Memory & Storage I/F 16-bit DDR4-1600 or DDR3L-1333 memory interfaces with in-line ECC; up to 4GB RAM Octal Peripheral Interface (OPI) for flash or […]