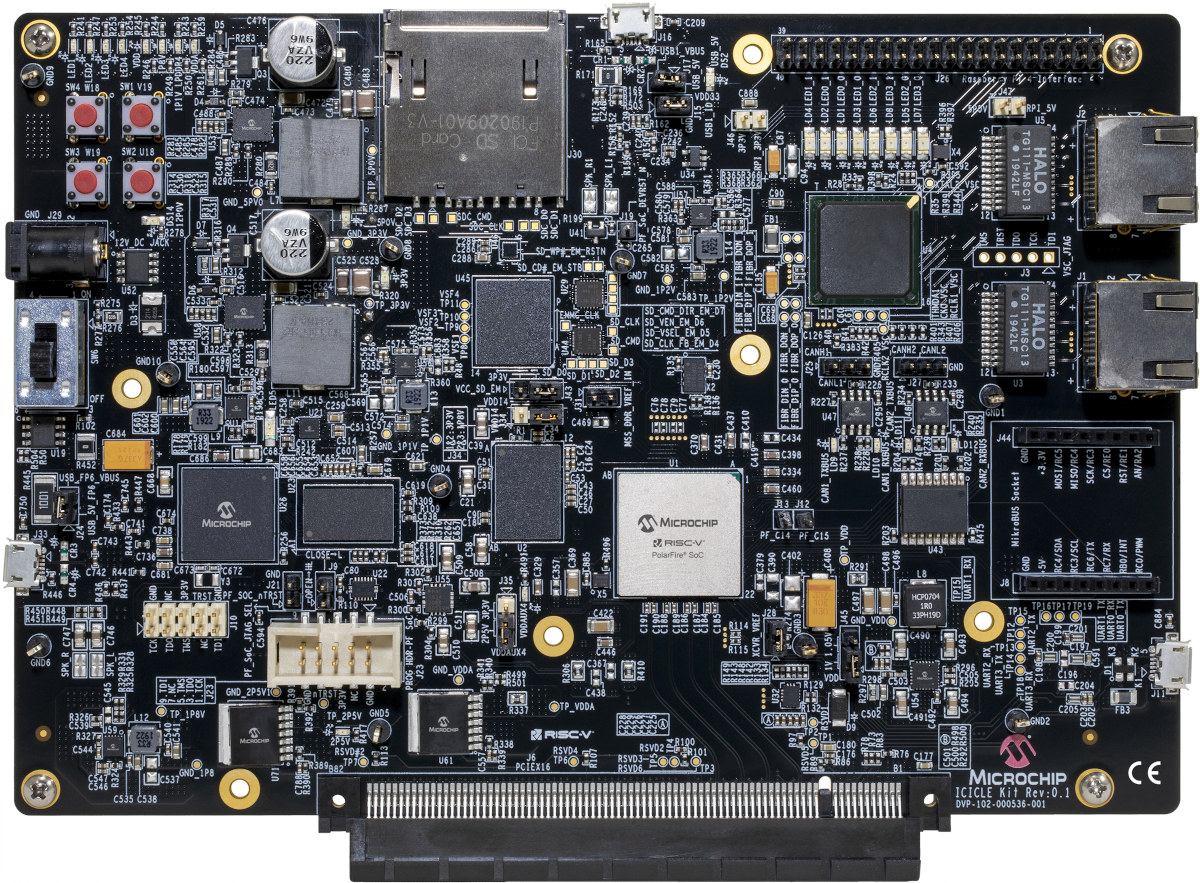

We got some more details about PolarFire RISC-V FPGA SoC late last year, and we were promised a Linux capable 64-bit RISC-V & FPGA development board with PolarFire SoC Icicle kit in Q3 of 2020. We are already in July 2020. So where is the board? Oh, look! It’s right here on Crowd Supply where it is offered for $499, and shipping is expected to start in mid-September. PolarFire SoC Icicle specifications: SoC FPGA – PolarFire SoC MPFS250T-FCVG484EES penta–core RISC-V CPU subsystem (1xRV64IMAC, 4xRV64GC) with 254K LE non-volatile fabric, 784 18 × 18 math blocks, secure boot, 4x 12.7 Gbps SERDES, FCVG484 package (19 × 19 mm, 0.8 mm pitch) System Memory – 2GB LPDDR4 x32 Storage – 1 GBit QSPI Flash, 8GB eMMC Flash or SD card slot (multiplexed) Video Output – HDMI 2.0 (removed from final board) Connectivity – 2x Gigabit Ethernet, Wi-Fi, and Bluetooth USB – 1x […]

Upcoming SAVVY-V Open Source RISC-V Cluster Board Supports 10GbE via Microsemi PolarFire 64-bit RISC-V SoC

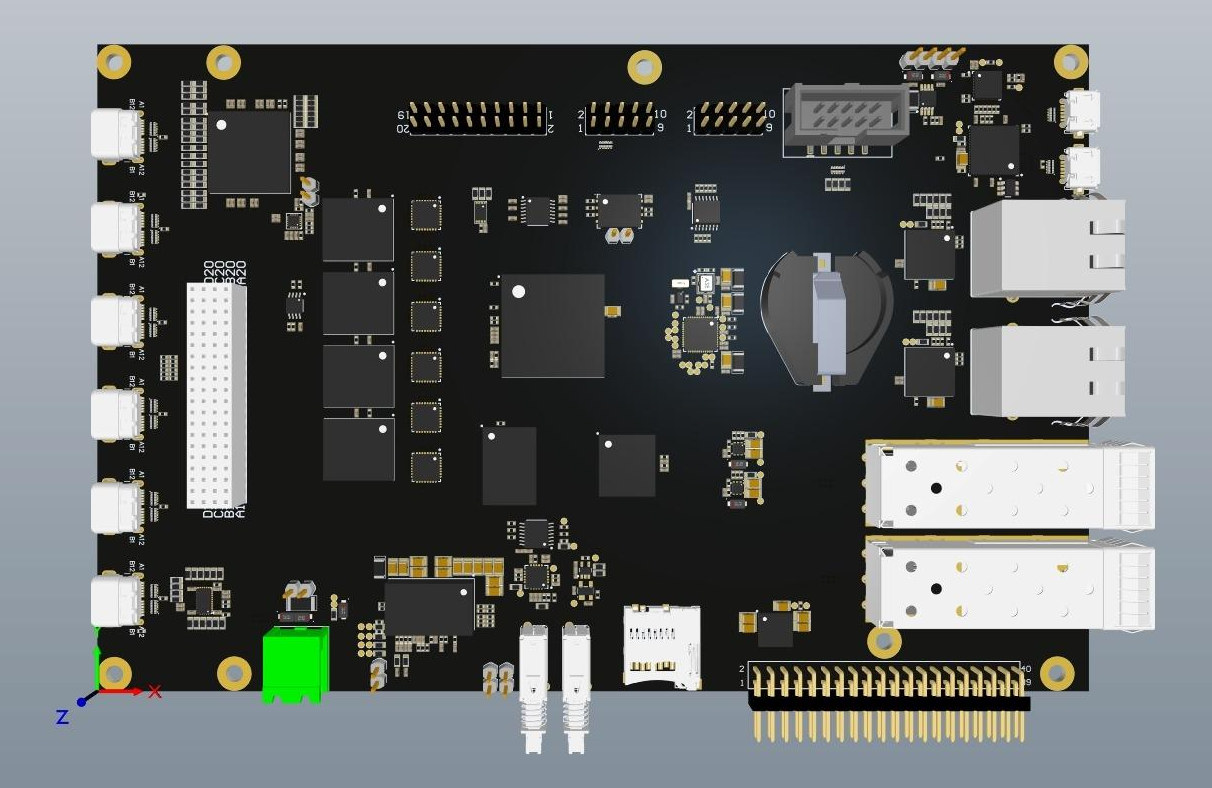

RISC-V based PolarFire SoC FPGA by Microsemi may be coming up in the third quarter of this year, but Ali Uzel has been sharing a few details about SAVVY-V advanced open-source RISC-V cluster board made by FOSOH-V (Flexible Open SOurce Hardware for RISC-V) community of developers. It’s powered by Microsemi Polarfire RISC-V SoC MPFS250T with four 64-bit RISC-V cores, a smaller RV64IMAC monitor core, and FPGA fabric that allows 10GbE via SFP+ cages, and exposes six USB Type-C ports. The solution is called a cluster board since up to six SAVVY-V boards can be stacked via a PC/104+ connector and interfaced via the USB-C ports. SAVVY-V cluster board preliminary features and specifications: SoC – Microsemi Polarfire RISC-V SoC MPFS250T with a quad-core 64-bit RV64IMAFDC (RV64GC) processor @ up to 667 MHz, a RV64IMAC monitor core, and FPGA fabric with 250K logic elements; 3.0 CoreMarks/MHz, 2.0 DMIPs/MHz; Also compatible with MPFS160T, […]

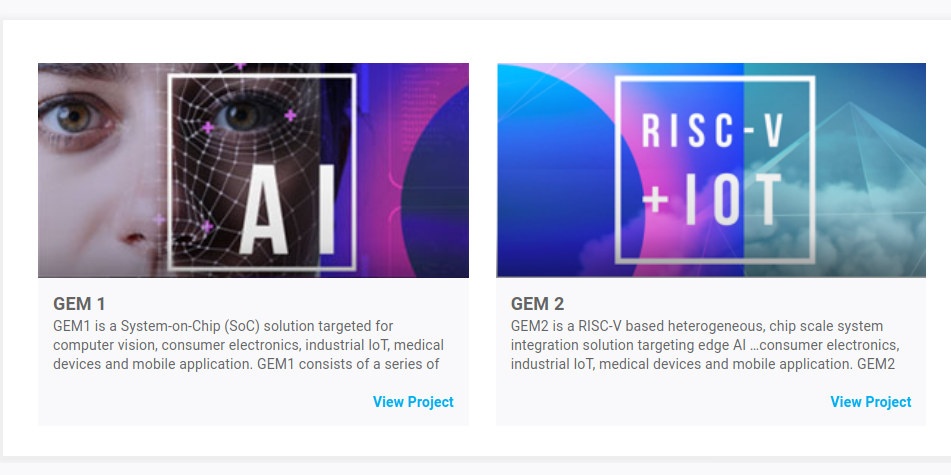

zGlue Launches the Open Chiplet Initiative in Collaboration with Google and Antmicro

We first covered zGlue’s ZiP (zGlue Integration Platform) in 2018 as the company introduced its multi-chip module similar to SiP (system-in-package) via a crowdfunding campaign. Just like SiP, the technology packages several components into a single package, but costs have been brought down to enable low-volume production of custom chips for a reasonable price. Since then the company announced new ZiP multi-chip modules such as nRF52832 based Omnichip and the FPGA, Arm or/and RISC-V based GEM ASIC by Antmicro. The company recently announced the Open Chiplet Initiative, a collection of open-source designs, tools and file formats, launched in collaboration with Google and Antmicro. There are four main types of tools within the Open Chiplet Initiative: Open Chiplet Interfaces – Currently only ZEF (zGlue Chiplet Info Exchange Format) is provided. It defined the part numbers, pins, and mechanical dimensions of various parts. The ZEF specification can be found on Github. Design […]

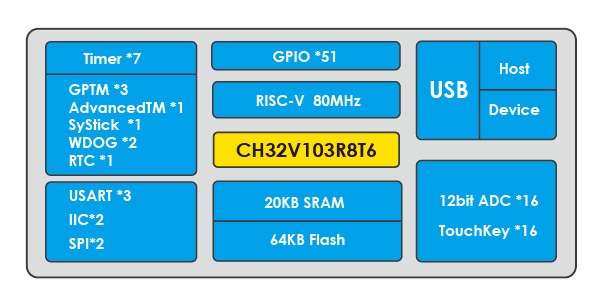

WCH CH32V103 General-Purpose RISC-V MCU Offers an Alternative to GD32V RISC-V Microcontroller

Last year, WCH introduced their first RISC-V MCU with CH572 Bluetooth LE microcontroller which came with 10KB SRAM and a not so convenient 96KB OTP flash. But I’ve just been informed the company has introduced their first general-purpose RISC-V MCU family with several CH32V103 microcontrollers featuring up to 64KB Flash and 20KB SRAM, and all sort of peripherals you’d expect from a general-purpose MCU. WCH CH32V103 key features and specifications: CPU Core – 32-bit RISC-V (RV32IMAC) core @ up to 72/80 MHz called ” RISC-V3A” Memory – 10KB or 20KB SRAM Storage – 32KB or 64KB flash Peripherals 1x USB 2.0 Full Speed Host/Device Up to 2x SPI (master/slave), up to 2x I2C, up to 3x USART Up to 16x 12-bit ADC/touch key 37x or 51x GPIOs Up to 3x general-purpose timers, 1x advanced timer, 2x watchdog timers, 1x Systick Supply Voltage – 2.7 to 5.5V Package – LQFP48, QFN48 […]

Linux 5.7 Released – Main Changes, Arm, MIPS and RISC-V Architectures

OK… I’m a bit late on that one. Linus Torvalds released Linux 5.7 last week: So we had a fairly calm last week, with nothing really screaming “let’s delay one more rc”. Knock wood – let’s hope we don’t have anything silly lurking this time, like the last-minute wifi regression we had in 5.6.. But embarrassing regressions last time notwithstanding, it all looks fine. And most of the discussion I’ve seen the last week or two has been about upcoming features, so the merge window is now open and I’ll start processing pull requests tomorrow as usual. But in the meantime, please give this a whirl. We’ve got a lot of changes in 5.7 as usual (all the stats look normal – but “normal” for us obviously pretty big and means “almost 14 thousand non-merge commits all over, from close to two thousand developers”), So the appended shortlog is only […]

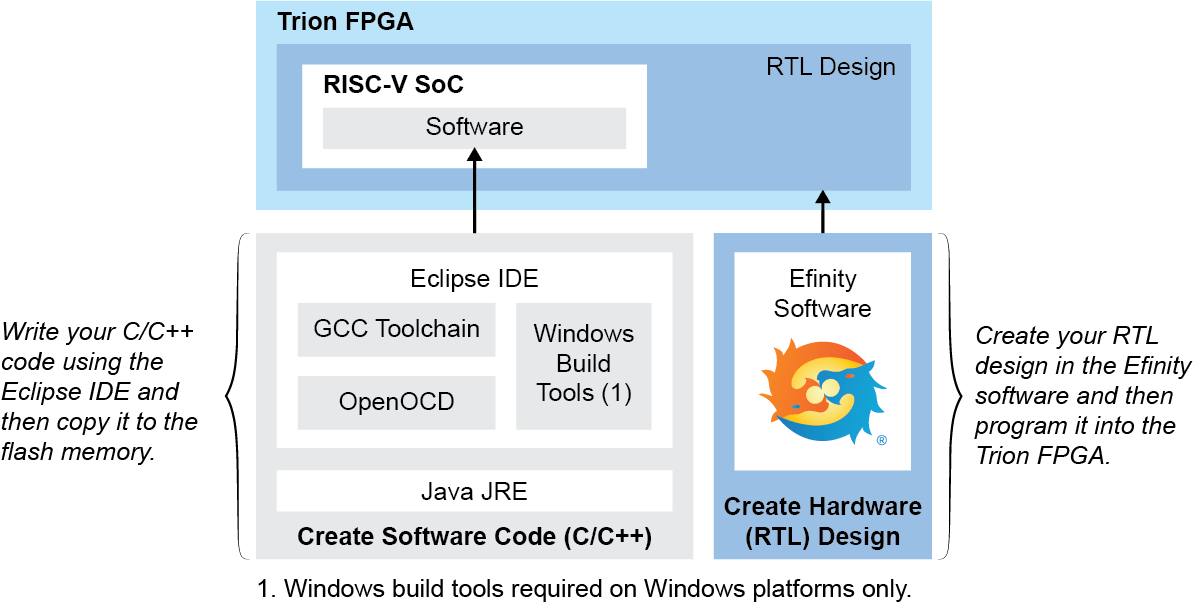

Efinix Releases Three RISC-V Software-Defined SoC’s Optimized for Trion FPGA’s

Efinix has announced three RISC-V Software-defined SoC’s based on Charles Papon’s VexRiscv core and optimized for the company’s Trion T8 to T120 FPGA’s. VexRiscv is a 32-bit RISC-V CPU using RISCV32I ISA with M and C extensions, has five pipeline stages (fetch, decode, execute, memory, and writeback), and a configurable feature set. Each SoC includes a RISC-V core, memory, as well as various I/O and interfaces. Key features for each of three RISC-V SoC’s: Ruby SoC FPGA footprint – ~12K LEs/78 RAM blocks Performance – 50 MHz (1.16 DMIPS/MHz) Memory – 4 KB on-chip RAM, up to 3.5 GB DDR DRAM Peripherals – 16x GPIO, Timer, PLIC, 3x SPI masters, 3x I2C masters/slaves, 2x UARTs 1x AXI4, 2x APB3 user peripherals Target applications – real-time system controls and image signal processing. Jade SoC FPGA footprint – ~7K LEs/93 RAM blocks Performance – 50 MHz (1.2 DMIPS/MHz) Memory – 32 KB […]

TTGO T-Watch K210 / K210 AIOT Watches Perform Face Detection with Kendryte K210 RISC-V Processor, ESP32 WiSoC

After covering ESP32 based TTGO T-Watch-2020 programmable watch last month, I noticed LilyGO launched “TTGO T-Watch K210 AIOT” watch with Kendryte K210 RISC-V AI SoC and a camera for face detection and recognition, and while searching for information, I discovered another apparently similar “TTGO T-Watch K210“. But let’s look into the specifications to find out what the differences are. I first came across TTGO T-Watch K210 AIOT, so let’s have a look at some preliminary specifications for this model: AI Processor – Kendryte K210 RISC-V Dualcore 64bit with FPU with 8MB SRAM Storage – 16MB QSPI flash, MicroSD card socket Display I/F – FPC connect for external display (not included) Camera – 2MP OV2640 sensor Audio – MAX98357A Audio codec; CVSD & SBC audio encoding Connectivity – 2.4 GHz 802.11b/g/n WiFi 4 up to 150 Mbps, Bluetooth 4.2 BR/EDR and BLE Debugging – USB-C port via CP2104 Expansion UART, SPI, […]

QEMU 5.0 Supports Recent Armv8.x Features, Cortex-M7 CPU, Host Directory Access, and More

QEMU (Quick EMUlator) is an open-source emulator that’s great to run programs on various architectures such as Arm, RISC-V, and many others when you don’t own proper hardware. The developers have now released QEMU 5.0.0 will plenty of new features and such as support for Armv8.1 to Armv8.4 architectures, Arm Cortex-M7 processor, various changes to MIPS, PowerPC, RISC-V, s390… architectures, support for accessing a directory on the host filesystem from the guest using virtiofsd and more. There have been over 2800+ commits from 232 developers, so the list of changes to too long to write here, but some of the highlights include: Support for passing host filesystem directory to guest via virtiofsd Support for ARMv8.1 VHE/VMID16/PAN/PMU, ARMv8.2 UAO/DCPoP/ATS1E1/TTCNP, ARMv8.3 RCPC/CCIDX, ARMv8.4 PMU/RCPC Added ARM Cortex-M7 CPU support New Arm boards: tacoma-bmc, Netduino Plus 2, and Orange Pi PC Allwinner SoC model now wires up the USB ports TPM support for […]