In the pool of 32-bit RISC-V microcontroller cores (E20 by SiFive, VEGA ET1031 by C-DAC), CloudBEAR showcased its 32-bit small and efficient MCU core – BM-310 at RISC-V GLOBAL FORUM 2020. CloudBEAR works on providing services like processor IP customization, support for RISC-V ISA extensions, product integration within a system-on-chip, and configurable instruction and data cache. Let’s first look into the CloudBEAR processor IP portfolio. It has three different product lines- BM series, BR series, and BI series. First, the BM series targets small and efficient MCUs cores. Second, the BR series targets fast and compact embedded cores. The third and most important BI series is about Linux capable application cores. In this article, we will look into the details of BM-310, which is the RISC-V MCU core for embedded and IoT solutions. BM-310 Architecture As RISC-V is a modular instruction set, extensions are optional for the developer. BM-310 architecture […]

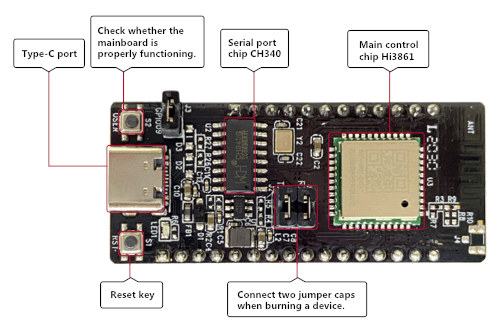

Hi3861 based HiSpark WiFi IoT development board supports LiteOS and HarmonyOS

HiHope HiSpark WiFi IoT development board features Hisilicon Hi3861 microcontroller with 2.4 GHz 802.11b/g/n WiFi 4 and supports Huawei LiteOS as well as HarmonyOS. Equipped with 2MB flash and 384KB SRAM, the board targets smart home applications, and ships with a baseboard to help with development. HiSpark board specifications: MCU – Hisilicon Hi3861 32-bit microcontroller @ up to 160 MHz with 352 KB SRAM and 288 KB ROM, 2 MB flash memory, and WiFI 4 connectivity; QFN-32 5x5mm package WiFi 802.11b/g/n standard up to 72 Mbps @ HT20 2.4 GHz frequency band (ch1-ch14). Station (STA) and access point (AP) modes with up to 6 clients for the latter WiFi mesh with up to 256 nodes Security – WPA, WPA2 personal, and WPS 2.0 PCB antenna USB – 1x USB Type-C port for power and programming via CH340 chip Expansion – 2x headers with up to 2x SPI, 2x I2C, 3x […]

Linux 5.9 Release – Main Changes, Arm, MIPS & RISC-V Architectures

Linus Torvalds has just announced the release of Linux 5.9 on lkml: Ok, so I’ll be honest – I had hoped for quite a bit fewer changes this last week, but at the same time there doesn’t really seem to be anything particularly scary in here. It’s just more commits and more lines changed than I would have wished for. The bulk of this is the networking fixes that I already mentioned as being pending in the rc8 release notes last weekend. In fact, about half the patch (and probably more of the number of commits) is from the networking stuff (both drivers and elsewhere). Outside of that, the most visible thing is a reinstatement of the fbdev amba-clcd driver – that’s a noticeable patch, but it’s basically just mainly a revert. The rest is really really tiny (mostly some other minor driver updates, but some filesystem and architecture fixes […]

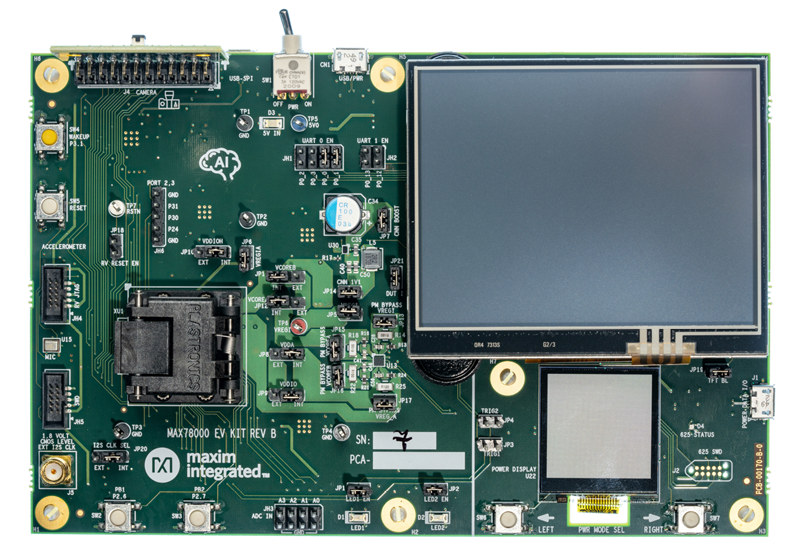

MAX78000 RISC-V & Cortex-M4F MCU enables IoT artificial Intelligence in battery-powered devices

Now even endpoints like sensors are capable of running basic artificial intelligence workloads thanks to microcontroller-class chips with built-in AI accelerators or instructions such as Kneron KL720 Arm Cortex-M4 AI SoC, GAP8 RISC-V IoT processor, or Cortex-M55 MCU core coupled with Ethos U55 MicroNPU. Maxim Integrated has now launched its own AI capable microcontroller with MAX78000 combining a Cortex-M4F core, a 32-bit RISC-V core, and a CNN accelerator enabling AI inferences at less than 1/100th the energy or 100 times the speed of software solutions making especially suited for battery-powered AI applications. MAX78000 specifications: Ultra-Low-Power microcontrollers Arm Cortex-M4F core with FPU Up to 100MHz with 512KB Flash and 128KB SRAM 32-Bit RISC-V ultra-low-power co-processor up to 60MHz Neural Network Accelerator optimized for Deep Convolutional Neural Networks (CNN) 442k 8bit Weight Capacity with 1,2,4,8-bit Weights Input Image Size up to 1024 x 1024 pixels Network Depth up to 64 Layers Layer […]

SiFive to Debut RISC-V PC for Developers based on Freedom U740 next-gen SoC

In recent years, people have discussed the need to have Arm-based PCs or workstations for developers to work directly on the target hardware, and there are now several options including SynQuacer E-Series 24-Core Arm PC, Ampere eMAG 64bit Arm Workstation, and HoneyComb LX2K 16-core Arm Workstation. Now it appears we’ll soon get something similar for RISC-V architecture with SiFive to debut the first RISC-V PC for developers at the Linley Fall Processor Conference 2020 taking place on October 20-22 and October 27-29. The PC will be powered by Freedom U740 next-generation RISC-V processor that will also be introduced at the event. We have very few details about this point in time, but the company points the SiFive Freedom U740 (FU740) SoC will enable professional developers to create RISC-V applications from bare-metal to Linux-based. The processor is said to combines a heterogeneous mix+match core complex with modern PC expansion capabilities, which […]

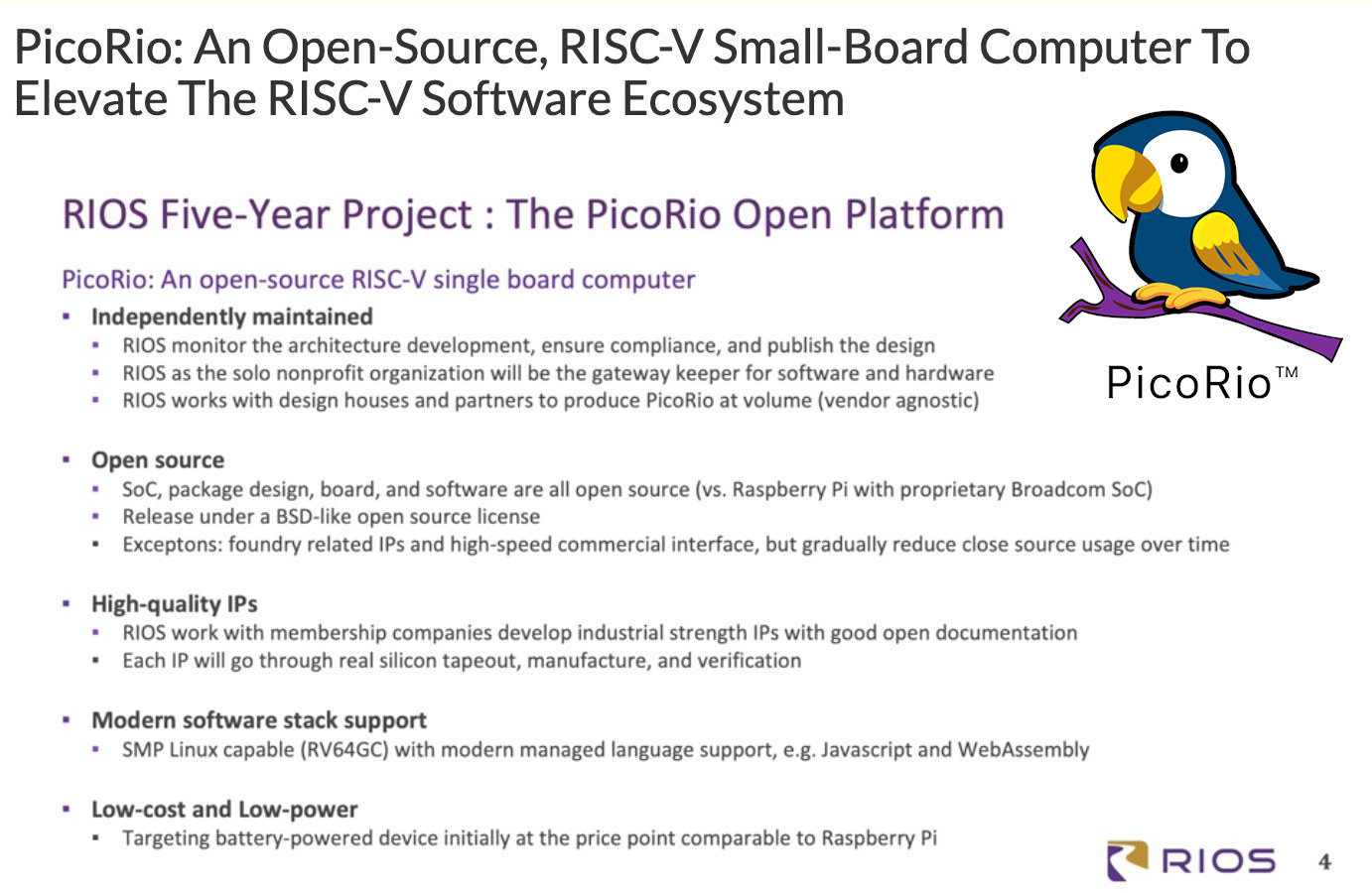

PicoRio Linux RISC-V SBC is an Open Source Alternative to Raspberry Pi Board

There’s a lot of interest/hype around RISC-V, and low-cost boards such as Longan Nano or Maixduino are already available, but those are based on microcontroller-class chips, even though it’s possible to run Linux on Kendryte K210 RISC-V board, it comes without MMU, so it’s not for everyone. Linux capable RISC-V boards do exist but cost several hundred dollars or more with the likes of HiFive Unleashed and PolarFire SoC Icicle development kit. If only there was a RISC-V board similar to the Raspberry Pi board and with a similar price point… The good news is that the RISC-V International Open Source (RIOS) Laboratory is collaborating with Imagination technologies to bring PicoRio RISC-V SBC to market at a price point similar to Raspberry Pi. The PicoRio board was presented at the RISC-V Global Forum on September 3rd. I could not find the full presentation slides yet, but there are some screenshots […]

RISC-V & ESP32 based TTGO Handheld T-WATCH K210 AIoT DevKit Works with a 9V Battery

LilyGO TTGO T-Watch K210 AIOT is a rather thick watch development kit based on Kendryte K210 RISC-V AI Processor and ESP32 WiSoC capable of performing AI workloads such as face detection using a USB power source. We first covered the development kit in June, and the company releases some small variants from time to time with the latest being TTGO Handheld T-Watch K210 with basically the same hardware, plus the addition of a handle that adds a power button, and a compartment for a 9V battery to power the watch/devkit. TTGO Handheld T-Watch K210 specifications: SoC – Kendryte K210 dual-core 64-bit RISC-V processor with 8MB RAM, AI accelerators Storage – 16MB flash, MicroSD card slot Display – 1.54-inch capacitive touch IPS screen connected over an 8080 interface Camera – Adjustable 2MP OV2640 sensor with 65-degree lens (optional 120-degree angle lens), AS312 “human” infrared sensor Connectivity – 2.4 GHz 802.11b/g/n WiFi […]

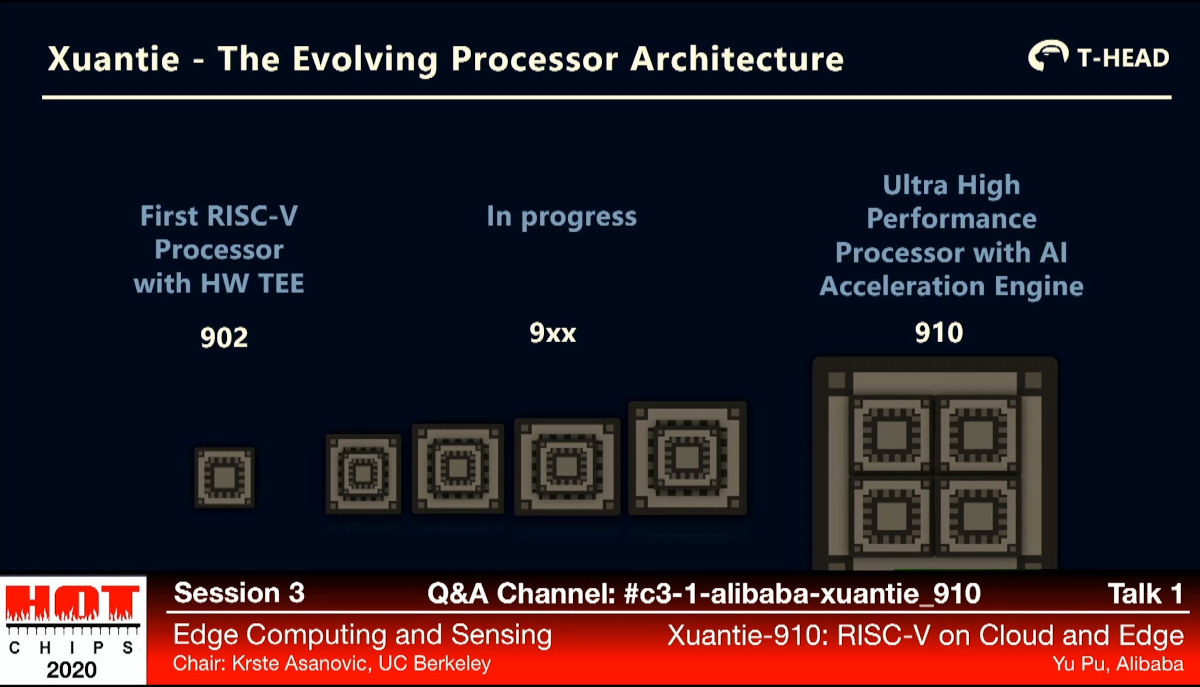

More Details about Alibaba XT910 64-bit RISC-V Core

Alibaba unveiled XuanTie 910 16-core RISC-V Processor last year with few details except it targetted high-performance 5G, AI, and autonomous driving applications. The company has now provided more details about Alibaba XuanTie 910 (aka XT910) processor during the virtual Hot Chips 2020 conference, and he notably compared the RV64GCV core found in the processor to Arm Cortex-A73 core. Alibaba XT910 main features and specifications: CPU – Up to 16x 64-bit RISC-V (RV64GCV) cores with RISC-V Vector extension and custom Turbo extension in four clusters of four cores; 12-stage out of order; Coremark: 7.1 per MHz Cache – 32KB or 64KB I/D cache per core, up to 8MB L2 cache per cluster FP16-FP64 floating-point unit Vector Computing Unit (aka Vector Engine) for AI acceleration Memory Management – Sv39 MMU + 8/16 PMP Interrupt Controller – Clint + PLIC Process – Final: 12nm FinFET; engineering samples: TSMC 28nm HPC Alibaba RISC-V Turbo […]