SiFive unveiled their Freedom U500 and E500 open source RISC-V SoCs last year, and a little layer launched HiFive1 Arduino compatible development board based on SiFive Freedom E310 processor. The company has now launched their non-open source Coreplex IP also based on RISC-V ISA with the 32-bit E31 Coreplex and 64-bit E51 Coreplex, and explained details about pricing.

Some of the key features of the processors are listed below:

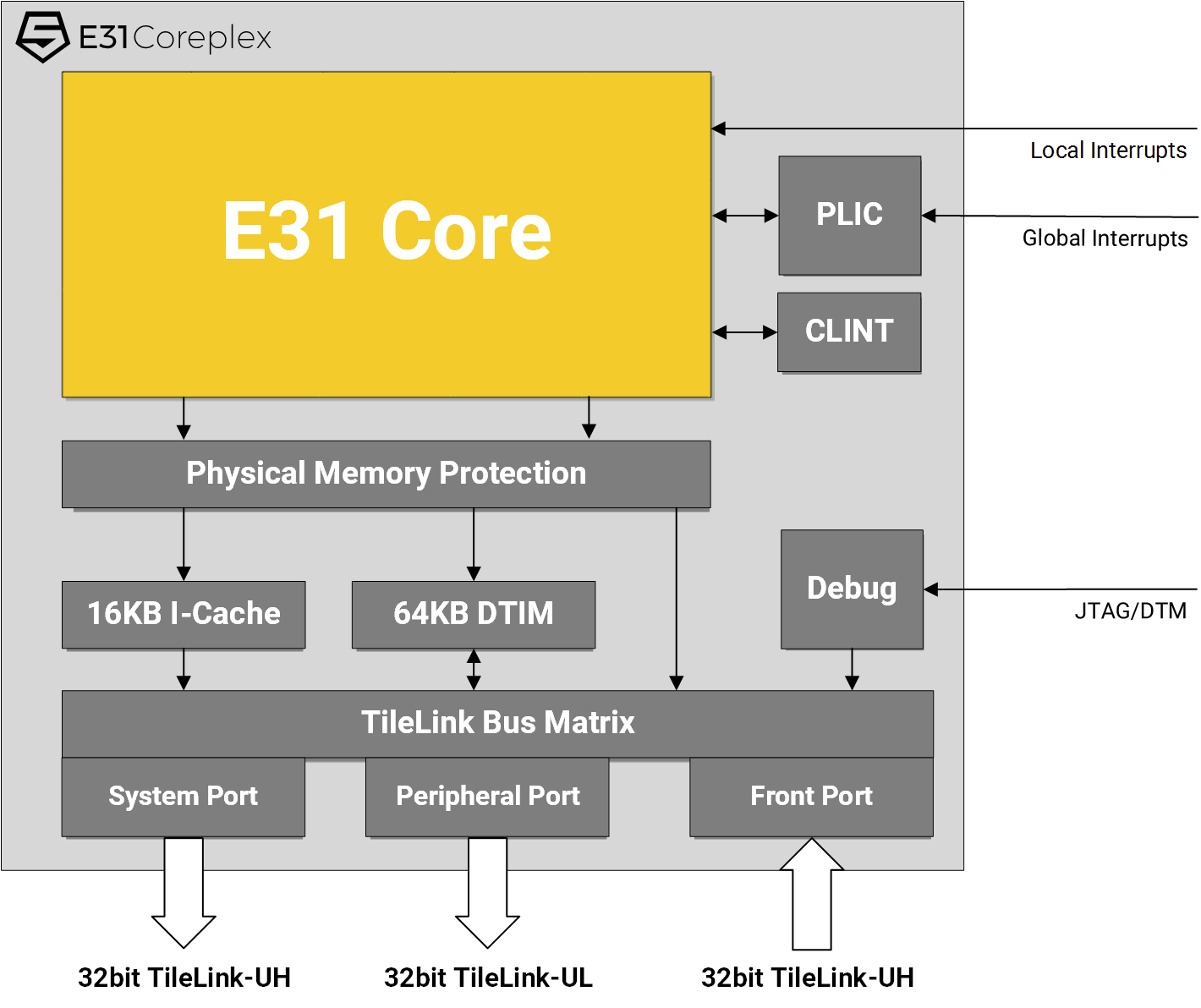

- E31 Coreplex

- 32-bit RV32IMAC core @ 900 to 1.5 GHz (with 28nm process)

- Advanced Memory Subsystem – 16KB, 2-way Instruction Cache, Instruction Tightly Integrated Memory (ITIM) option, up to 64KB Data Tightly Integrated Memory (DTIM) support

- Up to 16 local interrupts with vectored addresses

- Performance – 1.61 DMIPS/MHz ; 2.73 Coremark/MHz

- Power Consumption

- 28nm HPC process – Core only: 150 DMIPS/mW ; Coreplex: 41 DMIPS/mW

- 55nm LP process – Core only: 95 DMIPS/mW; Coreplex: 16 DMIPS/mW

- Applications: Edge Computing, Smart IoT or Wearables.

- Suited to replace the Cortex-M3 and Cortex-M4, but provides even higher performance without sacrificing area or power.

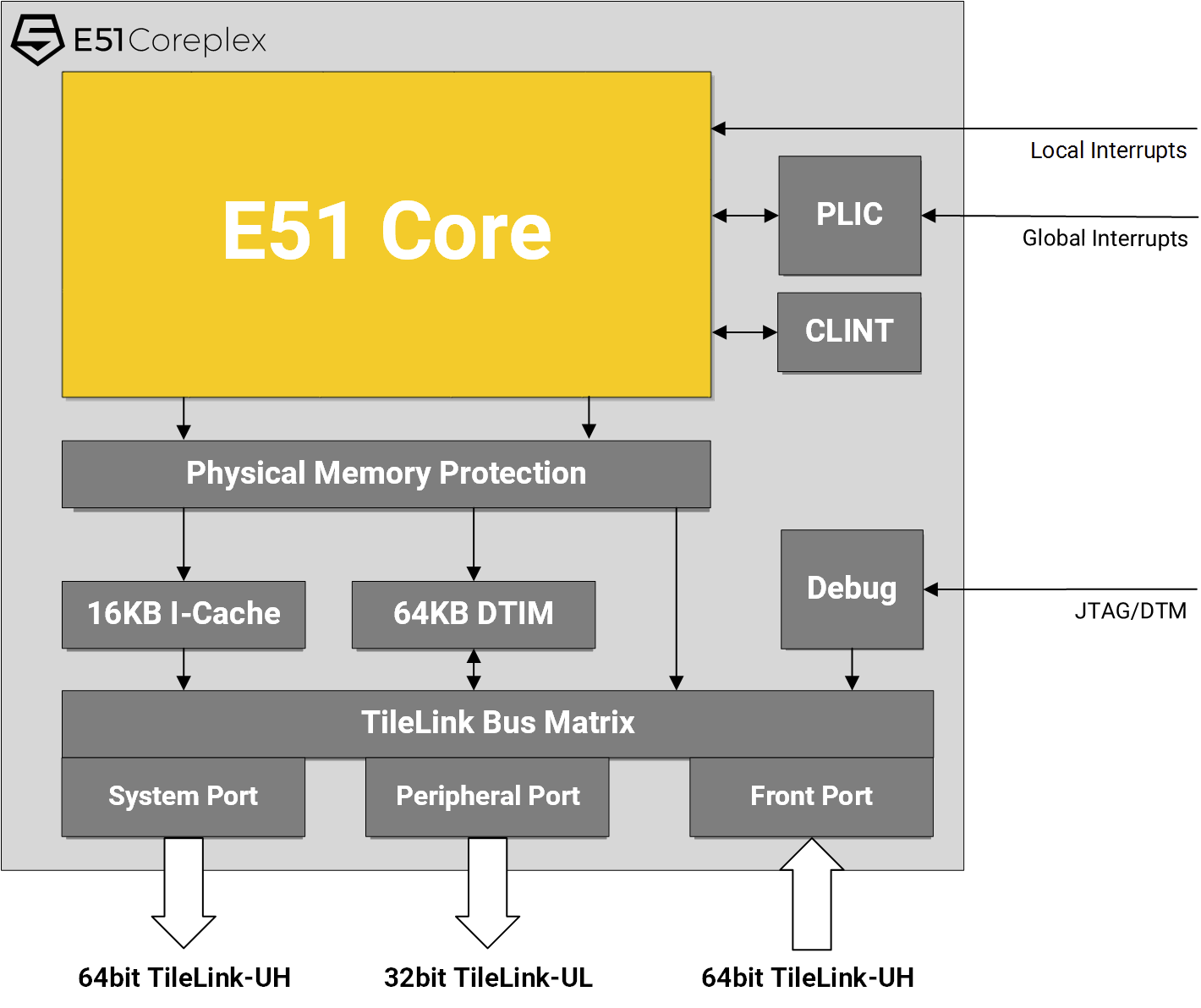

- E51 Coreplex

- 64-bit RV64IMAC embedded core @ 900 to 1.5 GHz (28nm process)

- Advanced Memory Subsystem – 16KB, 2-way Instruction Cache, Instruction Tightly Integrated Memory (ITIM) option, up to 64KB Data Tightly Integrated Memory (DTIM) support

- Support for up to 40 physical address bits

- Up to 16 local interrupts with vectored addresses

- Performance – 1.8 DMIPS/MHz ; 2.76 Coremark/MHz

- Power Consumption

- 28nm HPC process – Core only: 125 DMIPS/mW ; Coreplex: 36 DMIPS/mW

- 55nm LP process – Core only: 36 DMIPS/mW; Coreplex: 15 DMIPS/mW

- Applications:

- System or host control core within a larger 64-bit SoC

- SSD controllers and network processors which require 64-bit compute without the requirement of virtual memory or full-featured operating systems.

If you want to manufacture an ARM processor, you first need to buy a license before accessing any information, and once you’re shipping your chips, you’ll pay royalties for each SoC sold with one or more ARM cores. SiFive business model is different. First, it’s free to try Coreplex IP on FPGA boards such as Digilent Arty, or evaluate RTL code in your own environment, so you don’t need to commit to any large investment before knowing whether you’ll go ahead with the cores. SiFive Coreplex IP is also royalty-free so how much you pay does not depend on how many chips you sell, and the way they make money is through a one-time license that costs $275,000 and up for E31 Coreplex, and $595,000 and up for E51 Coreplex with the exact price depending on options.

You’ll find the full details on Sifive Coreplex IP product page.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress. We also use affiliate links in articles to earn commissions if you make a purchase after clicking on those links.

…wasn’t RISC-V intended to be fully OSS?

@TC the ISA/specs/reference implementation are, but you can make a compatible chip with different implementation and use the ISA for free

When will they make one with an mmu

@parrotgeek1

It has hardware memory protection, does it really need address translation? That adds complexity, a performance penalty and increases power usage.

I guess you need a full MMU if you’re going to implement virtual memory, but with today’s memory sizes it feels like an anachronism, or an excuse for programmers to be wasteful with memory.