Last year, SiFive introduced their first RISC-V cores competing with Arm Cortex-R family of processors thanks to their S7 Series 64-bit RISC-V Core IP providing an answer to Arm Cortex-R7/R8 32-bit real-time processors.

The company has now announced the SiFive S2 RISC-V core that it claims to be the world’s smallest 64-bit embedded core, and also the first SiFive IP core without any direct competitive equivalent in the market.

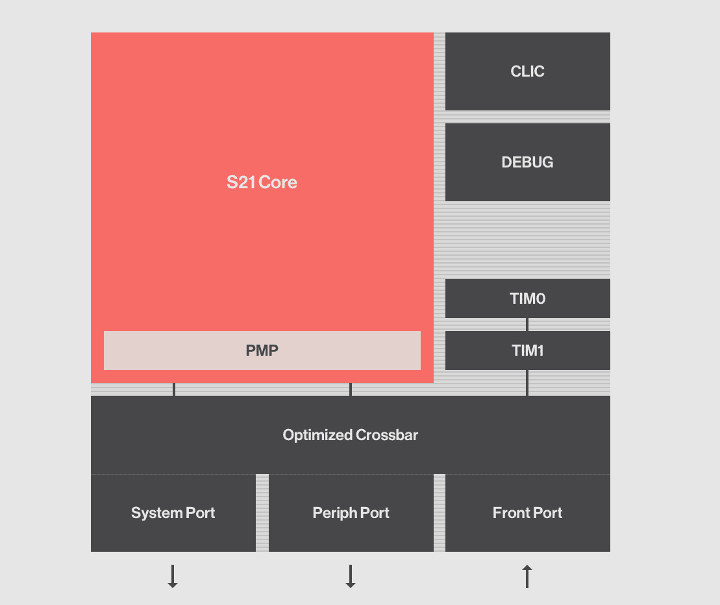

For now, there’s only one core in the family with SiFive S21 offering the following key features:

For now, there’s only one core in the family with SiFive S21 offering the following key features:

- RISC-V ISA – RV64IMAC

- 64-bit AXI Ports

- Machine and User Mode with 4 Region Physical Memory Protection

- 3-stage pipeline with Simultaneous Instruction and Data Access

- 2 Banks of Tightly Integrated Memory (TIM)

- CLIC (Core Local Interrupt Controller) with 127 interrupts

- Advanced debug with 4 hardware breakpoints/watchpoints

- Performance – 1.6 DMIPS/MHz; 3.2 Coremarks/MHz

The company compares its to the SiFive S5 cores, which I had not heard about previously, and are competing with Arm Cortex-R4/R5 cores. SiFive S2 is just half the size of a similarly configured S5 core, and as such is particularly well suited for area constrained applications demanding a 64-bit processor.

That means S2 may be found in 64-bit Embedded Controllers, consumer applications, industrial automation, or integrated as a management core as part of a more complex SoC.

More details may be found in the product page.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress. We also use affiliate links in articles to earn commissions if you make a purchase after clicking on those links.

I was reading yesterday about ” Taiwan asic design house Faraday Technology is offering RISC-V processor IP for chips aimed at AI and IoT.

“This solution encompasses system-level design services, such as RISC-V core IP integration, SoC design verification, as well as a reference design kit consisting of RTOS and peripherals drivers,” said the firm, adding that it has already enabled mass production of RISC-V based AI SoCs on UMC’s 55ULP process. aimed at battery-powered IoT edge devices. ” at electronicsweekly. Good to see more and more usage and growth of RISC-V

Faraday used to make ARMv4 cores like the FA526. Their CPU team was spun out into Andes, who went on to make their own nds32 RISC architecture, and more recently became known for their RISC-V cores. While the Faraday announcement mentions nothing of this, and Andes does not disclose who they licenses their cores, I would guess that the two companies are cooperating closely on this.

MAC is a list of ISA options, I think. M: integer Multiply, and divide. A: Atomic instructions. C: Compressed instructions.

If I understand correctly, this doesn’t have an MMU and so would not run Linux well. I think that the MMU option would go by a name like SV48.