At the end of last month, there was a lot of buzz about Bouffalo BL602, one of the first RISC-V SoC with built-in wireless connectivity, namely WiFi 4 and Bluetooth 5.0 LE.

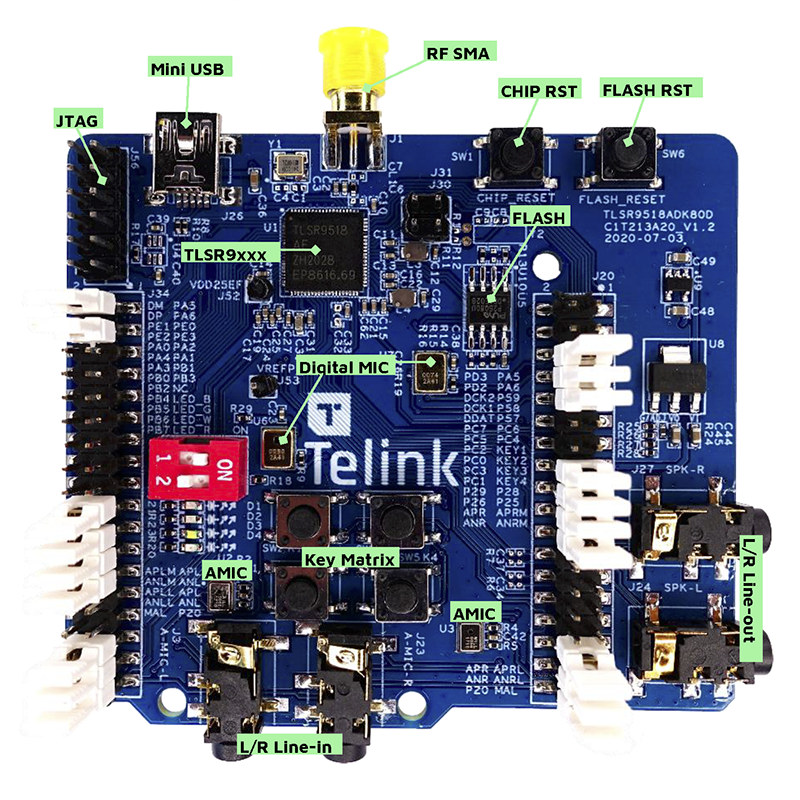

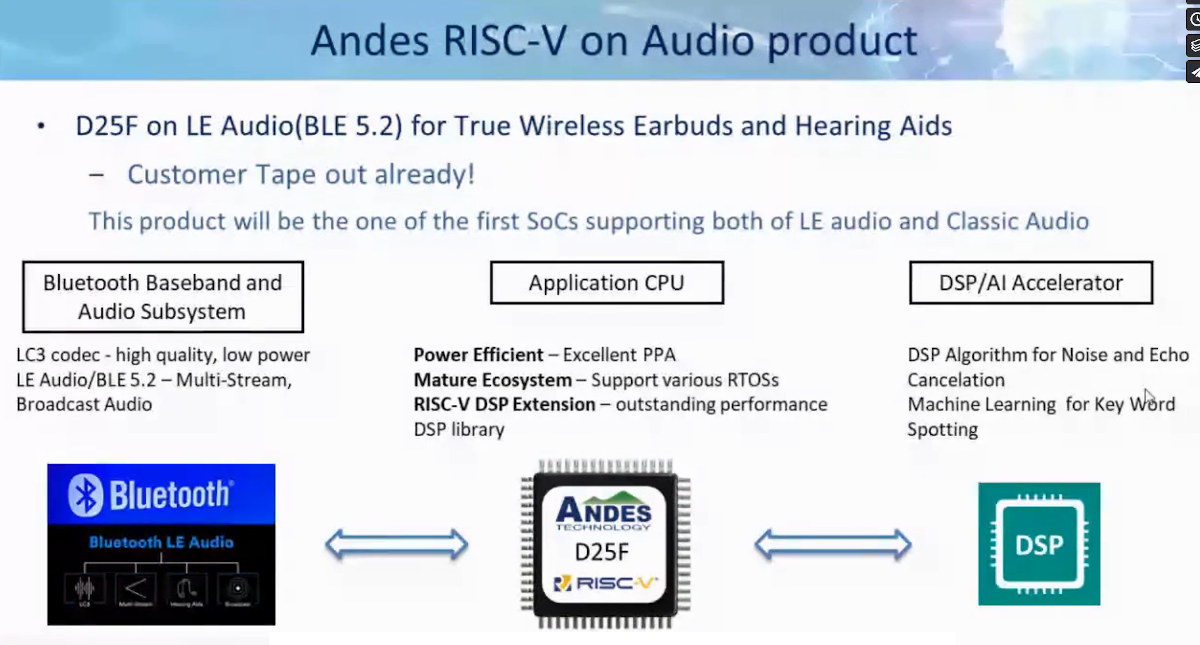

We should expect more and more of those types of solutions, and Telink & Andes jointly introduced TLSR9-series of wireless audio chips for hearables, wearables, and other high-performance IoT applications. The chips are powered by an Andes D25F RISC-V 5-stage core that happens to be the first core to integrate RISC-V DSP/SIMD P-extension and offer Bluetooth 5.2, Zigbee 3.0, HomeKit, 6LoWPAN, Thread, and/or 2.4 GHz proprietary protocol.

The press release focuses on the Andes core, but an article in Chinese allows use to find more about Telink TLSR9 family’s key features:

- CPU – Andes D25F 32-bit RISC-V 5-stage core @ up to 96 MHz (2.59 DMIPS/MHz and 3.54 CoreMark/MHz) with RISC-V DSP/SIMD P-extension

- Optional NNU – AI engine supporting DNN, LSTM, and RNN neural networks

- Memory/Storage – 256KB SRAM and 1 MB to 2MB Flash

- Connectivity

- Bluetooth 5.2 BR/EDR/LE with long-range, indoor positioning, BLE Mesh support

- Zigbee 3.0

- HomeKit

- 6LoWPAN

- Thread

- 2.4 GHz proprietary protocol

- Audio

- SBC, OPUS, AAC, and LC3 audio codecs

- Echo cancellation, noise reduction. Optional active noise reduction (ANC) and multi-microphone environmental noise reduction (ENC).

- Peripherals – ADC, PWM, USB, I2C, SPI, UART, GPIOs…

- Security – AES, elliptic curve ECC, true random number generator; secure boot mechanism on higher-end models

- Debugging – 2-wire SWD or 5-wire JTAG debugging interface

- Power Management – Various low-power modes

- Packages – QFN, BGA

Software development is done through IAR Embedded Workbench for RISC-V (EWRISC-V) tools, or a free Eclipse-based IDE with supports for GDB and OpenOCD debug tools, GCC and LLVM toolchains, and more. RTOS are also supported including FreeRTOS.

The company claims using RISC-V P-extension (RVP) makes the compact AI/ML applications possible on the edge devices with, for instance, a 14.3x speedup reported for CIFAR-10 AI models (image classification), and 8.9x speedup of keyword spotting technology. Besides the higher performance, the P-extension can also enable significant lower power-consumption since the system could run at a lower clock speed for the same performance.

If you want to learn more about Telink TLSR9 and Andes D25F core, both were discussed during a RISC-V Day in Vietnam. The part about TLSR9/DR25F starts at the 7:29:42 mark.

I could not find any information on Telink Semiconductor website about the TLSR9 family, but the Telink Wiki has information about earlier TLSR8 chips, and one may expect it to be updated for the new chips sooner or later.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

Some availability information:

Mini USB, lol. That’s the Chinese way to say: We cobbled together an as cheap as possible devkit, so you can build as cheap as possible gadgets.

Nevermind. We all love and admire the ambition of Chinese developers to save money 😉

We do and I don’t mind mini USB. I mean I got enough mini USB and micro USB cables here. As well as USB-C. If they can get mini USB for 1 cent instead of 20 cents, go for it 😀

I think a lot of people forget how robust the mini USB connectors are. Sure, they’re no longer mainstream, but indeed, why does this need USB-C? It’s a dev kit, not a consumer product.

Their _lack_ of robustness was a large part of why they were deprecated! This is compounded by the failing part being on the connector, not the cable, making for harder failures. Mini USB _is_ a bad choice.

Mini USB isn’t failing as much as micro USB. Micro USB is the worst. And the most failures happen at the SMD solder joints. This is something which is problematic for all kind of connectors. People press against it. Over and over. And of course this is too much stress for the solder joints.

Huh? What the heck were you doing with your device? I’ve had far more micro USB connector failures at both ends. I can’t say I have had a single mini USB device go bad at the connector ends.

This is a religious topic, either you are for the one or the other connector…

I agree that they are robust but as KarlIP mentioned the main issue is the part that fails is the connector not the cable unlike Type C and Micro USB where it’s designed in such a way the cable fails while the connector doesn’t.

But I’ve definitely had several Micro USB connectors fail.

I have had a lot of problems with the micro USB connectors failing, so sorry, I can’t agree on this at all. Never had mini USB connectors fail.

I never had troubles with the flimsi micro, but got struck of several bad, under dimensioned mini cables for ext. HDDs and card readers, which keeps mini in bad memories, even though mechanically micro should be more error prone than mini…

And I better won’t start about the numerous incompatibilities of that time, i.e. can’t charge a moto phone with a charger that doesn’t come with some weird strapping resistors, so maybe not the connector is bad, but connected with bad memories of the early times of USB.

Telink isn’t a Chinese company though, they’re US/Taiwanese, with the engineering done in China. Their HQ is in Santa Clara. But please, let us really know what you think about a company you don’t know the first thing about.

Depends on the definition. China is still representing Taiwan in the UN ^^

Seriously? Can we not have a political discussion here?

one more chinese IC company, one more risc-v+AI chip. Great!

Again, not Chinese, US/Taiwanese. Please stop assuming every company you haven’t heard of is from China. I have visited their office in Taipei several times and it’s a very friendly bunch of people. Their development tools need some work, but their pricing is unbeatable.

A bit off topic but that video was posted by Shumpei Kawasaki.. I seem to remember him being involved with j-core (Open source SuperH). I wonder if it’s the same guy and if so does that mean j-core is deader than it seemed to be.

At 2:41, there is a picture with history of their proposed architecture, with SUPER-H2 as oldest proposed one, in 2006~2011.

These audio chips support 16bit/192khz or 24bit/192khz?