Arm has introduced a new MCU-class core with the Cortex-M85 core that offers higher integer performance than Cortex-M7, and higher machine learning performance compared to Cortex-M55 equipped with Helium instructions.

The new Cortex-M85 core is designed for developers requiring increased performance for their Cortex-M powered products without going to Cortex-A cores, and instead, keeping important features such as determinism, short interrupt latencies, and advanced low-power management modes found in all Cortex-M cores.

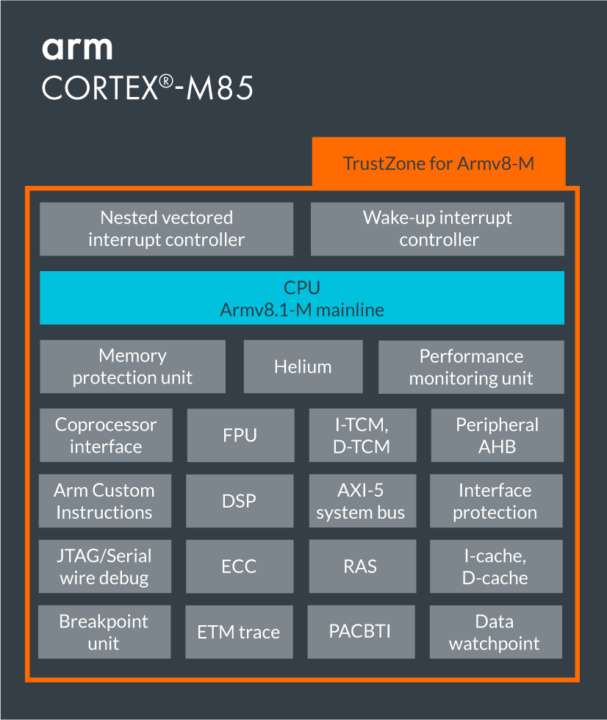

Arm Cortex-M85 key features and specifications:

- Architecture – Armv8.1-M

- Performance efficiency – 6.28 CoreMark/MHz and 3.13/4.52/8.76DMIPS/MHz (1. “ground rules” in the Dhrystone documentation, 2. inlining of functions, 3. simultaneous (”multi-file”) compilation).

- Bus interfaces

- AMBA 5 AXI 64-bit Main system bus (compatible with AXI4 IPs)

- AMBA 5 AHB 32-bit Peripheral bus

- AMBA 5 AHB 64-bit TCM Access bus (subordinate port)

- Pipeline – 7-stage (for main integer pipeline)

- Security

- Arm TrustZone technology

- PACBTI extension (Pointer Authentication, Branch Target Identification) helps in achieving PSA Certified Level 2 security.

- Memory Protection – Optional Memory Protection Units (MPU) for process isolation with up to 16 MPU regions and a background region – if TrustZone is implemented, there can be a Secure and a Non-secure MPUs.

- DSP extension – 32-bit DSP/SIMD extension

- Vector extension

- Optional Helium technology (M-profile Vector Extension) supporting up to:2 x 32-bit MACs/cycle

- 4 x 16-bit MACs/cycle

- 8 x 8-bit MACs/cycle

- Floating-point Unit (FPU) – Optional FPU with support for half-precision (fp16), single precision (fp32) and double precision (fp64) floating-point operations.

- Accelerator support – Optional coprocessor interface (64-bit) supporting up to 8 coprocessor units for custom compute accelerators. Optional Arm Custom Instructions.

- Instruction cache – Up to 64kB with ECC (optional)

- Data cache – Up to 64kB with ECC (optional)

- Instruction TCM (ITCM) – Up to 16MB with ECC (optional)

- Data TCM (DTCM) – Up to 16MB with ECC (optional)

- Interrupts

- Integrated Nested Vectored Interrupt Controller (NVIC) supporting up to 480 interrupts, and Non-maskable interrupt (NMI). Number of priority levels configurable from 8 to 256.

- Wake-up Interrupt Controller (WIC)

- Internal and/or external (optional) WIC for waking up the processor from state retention power gating or when all clocks are stopped

- Low power support

- Architecturally defined Sleep and Deep Sleep modes.

- Integrated wait for event (WFE) and wait for interrupt (WFI) instructions with Sleep On Exit functionality

- Sleep and Deep Sleep indication signals

- Multiple power domains with optional retention support for memories and logic

- Debug

- Hardware and software breakpoints

- Performance Monitoring Unit (PMU)

- Trace – Optional Instruction trace with Embedded Trace Macrocell (ETM), Data Trace (DWT) (selective data trace), and Instrumentation Trace (ITM) (software trace)

- Robustness

- ECC on instruction cache, data cache, instruction TCM, data TCM (optional)

- Dual-core lockstep (optional, available by the end of 2022)

- Bus interface protection (optional, available by the end end of 2022)

- PMC-100 (Programmable MBIST Controller, optional, available by the end of 2022)

- Reliability, availability, and serviceability (RAS) extension

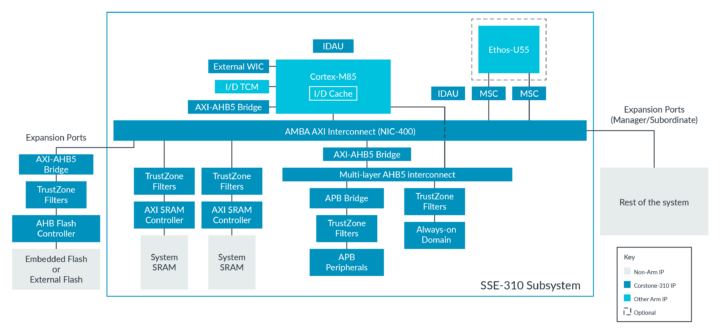

- Reference package – Corstone-310 with Cortex-M85 and Ethos-U55 uNPU

Designers can start with the Arm Corstone-310 (SSE-310) subsystem reference platform combining the Cortex-M85 and the Ethos-U55 uNPU, and other elements to make a microcontroller with SRAM, Trustzone, power control kit (PCK-600), secure debug component (SDC-600), security-aware system IP components of the SIE-200. Software developers can also prepare their code for the new core using Arm Virtual Hardware (AVH) with models of Arm-based processors, systems, and development boards, including the Corstone-310 to enable prototyping, development, and deployment.

Cortex-M85 based microcontroller will come with larger on-chip SRAMs, higher clock speeds (probably meaning we’ll see more 1GHz+ microcontrollers beyond just NXP i.MX RT1170), and implemented in smaller geometry nodes, with Arm providing a Cortex-M85 PIK (Processor Implementation Kit) with TSMC 22ULL foundry process that includes a user guide, shmoo plots, floorplans, and reference implementation scripts in one package.

Arm did not say when we can expect Cortex-M85 microcontrollers, but there can be a lag of one or two years after an Arm core is announced for silicon from partners to become available. More details may be found in the announcement and the developer page.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress. We also use affiliate links in articles to earn commissions if you make a purchase after clicking on those links.

So, about 5 years from now we will see an implementation that isn’t a probable scam or so secretive, that even manufacturer does not advertise its presence on SoC anymore.

Renesas RA8M1 is the first Cortex-M85 MCU:

https://www.cnx-software.com/2023/10/31/renesas-ra8m1-world-first-arm-cortex-m85-microcontroller/