MYIR has introduced the MYC-J1028X CPU module based on NXP LS1028A dual Cortex-A72 processor with time-sensitive networking (TSN) support, as well as the MYD-J1028X development board with five Gigabit Ethernet ports, and other interfaces to evaluate the solution.

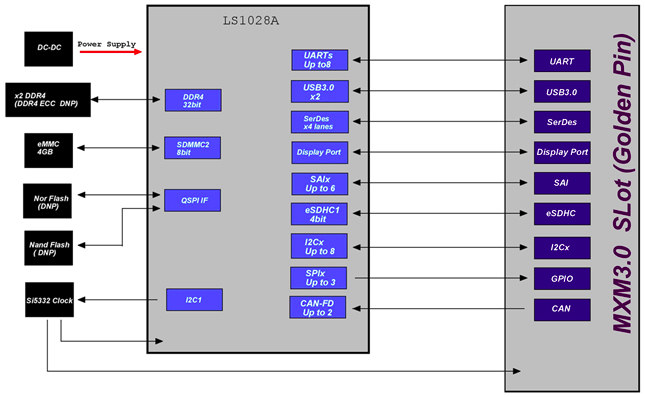

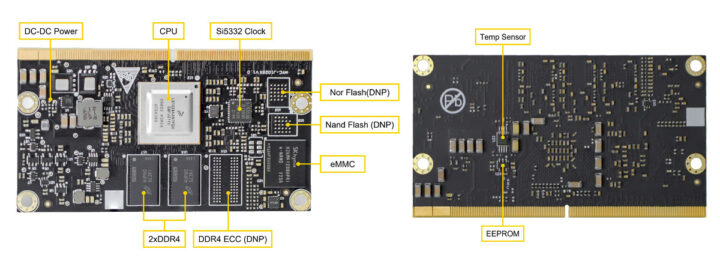

The MYC-J1028X is equipped with 2GB DDR4, 8GB eMMC flash, a 32Kbit EEPROM, and a temperature sensor by default, and exposes all I/Os through a 314-pin MXM 3.0 edge connector. The module also comes with footprints to solder a QSPI NAND Flash, XSPI NOR Flash, and/or ECC memory. Typical applications include industrial routers, industrial control, edge computing, automotive electronics, industrial IoT, and more.

MYC-J1028X CPU module

MYC-J1028X SoM specifications:

- SoC – NXP Layerscape LS1028A (LS1028AXN7PQA) dual-core Cortex-A72 processor @ 1.5 GHz with 3D GPU, integrated TSN Ethernet switches and Ethernet controllers

- System Memory – 2GB DDR4 (optional 3GB / 4GB DDR4); optional DDR4 ECC

- Storage

- 8GB eMMC flash (optional 16GB / 32GB)

- QSPI NAND Flash (not populated by default)

- XSPI NOR Flash (not populated by default)

- 32Kbit EEPROM

- 314-pin MXM 3.0 edge connector with

- Storage – 1x SATA 3.0

- Display I/F – 1x DP1.3/eDP1.4 up to 4Kp60

- Audio – 6x SAI

- Networking (SerDes) – 1x SGMII, 1x QSGMII

- USB – 2x USB 3.0

- Serial – 2x UART, 6x LPUART, 2x CAN-FD

- 2x PCIe 3.0

- 2x SDIO

- Low speed I/Os – 8x I2C, 3x SPI, GPIOs

- Debugging – 1x JTAG

- Misc – Temperature sensor

- Power Supply – 5V/2A

- Dimensions – 82 x 45mm (12-layer PCB)

- Temperature Range – -40 to 85°C (industrial grade)

MYiR provides a Ubuntu 18.04 with Linux 5.4.47 and a Yocto 3.2.1-built “Real-time Edge” image with Linux 5.10.9. Both with a complete SDK with open-source drivers available to customers, or in other words, not public.

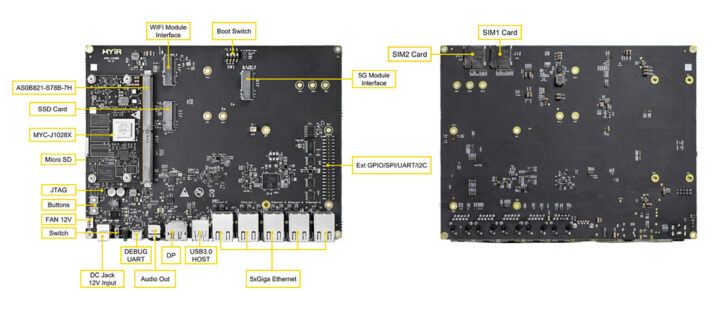

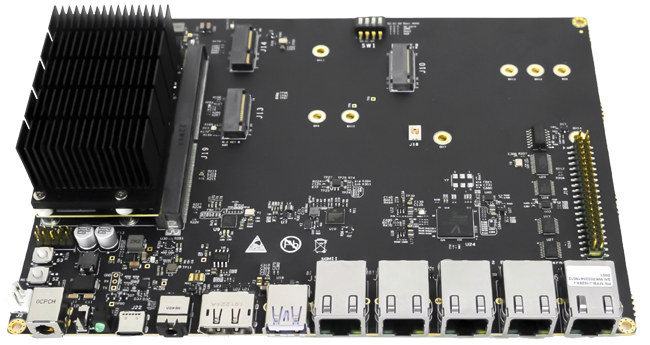

MYD-J1028X development board

- SoM – MYiR MYC-J1028X as described above, and fitted with a thick heatsink

- Storage

- M.2 Key B SATA 3.0 socket

- MicroSD card slot

- Video Output – DisplayPort up to 4Kp60

- Audio – 3.5mm audio jack

- Networking

- 5x Gigabit Ethernet RJ45 ports with TSN support

- Optional WiFi via M.2 socket (See Expansion section)

- Optional 5G module via M.2 socket (see Expansion section) + 2x SIM card slots

- USB – 1x USB 3.0 Host port

- Expansion

- 40-pin Raspberry Pi-compatible expansion header with GPIO, SPI, 2x UART, I2C and supporting MY-WIREDCOM RPI RS485, RS232 and CAN module

- M.2 Key B socket (USB 3.0) for optional 5G module

- M.2 Key E PCIe 3.0 socket for optional WiFi module

- M.2 Key B SATA 3.0 socket

- Debugging – Debug UART (TTL, USB Type-C connector)

- Misc – Power switch, reset and user buttons, power LED

- Power Supply – 12V/2A via DC jack

- Dimensions – 200mm x 150mm (4-layer PCB)

- Temperature Range – -40 to 85°C (industrial grade)

MyIR MYC-J1028X LS1028A CPU module is sold for $179 for single unit orders in its default configuration, and the MYD-J1028X development board goes for $279 with the baseboard, module, USB cable, 12V/2A power adapter, and a Quick Start Guide. You’ll find more details and purchase links on the product page.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress. We also use affiliate links in articles to earn commissions if you make a purchase after clicking on those links.

Hum.

Another laugh-and-forget board.