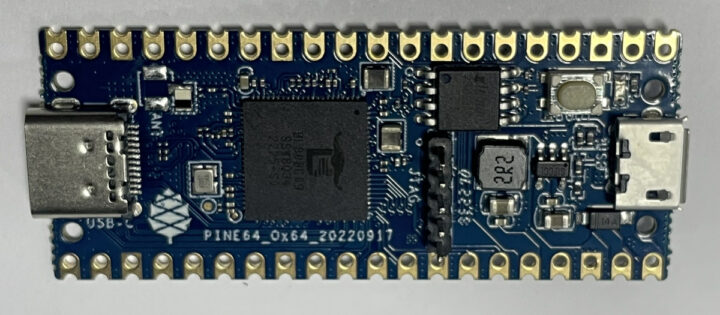

Pine64 Ox64 is a single board computer powered by Bouffalo Lab BL808 dual-core 64-bit/32-bit RISC-V processor with up to 64MB embedded RAM, multiple radios for WiFi 4, Bluetooth 5.0, and 802.15.4 (Zigbee), as well as an AI accelerator.

The board also features up to 16MB XSPI NOR flash, a MicroSD card socket, a USB 2.0 OTG port with support for a 2-lane MIPI CSI camera module, and two 20-pin GPIO headers for expansion. It measures just 51 x 21mm, or in other words, is about the size of a Raspberry Pi Pico W.

Pine64 Ox64 specifications:

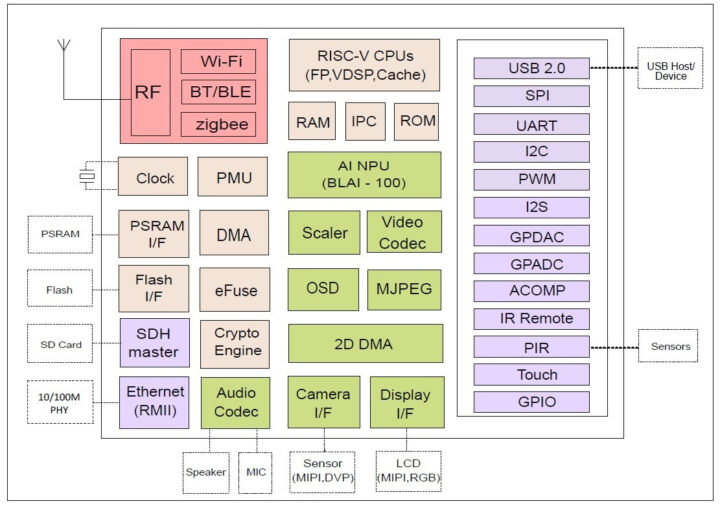

- SoC – Bouffalo Lab BL808 with:

- CPU

- Alibaba T-head C906 64-bit RISC-V core @ 480MHz

- Alibaba T-head E907 32-bit RISC-V core @ 320MHz

- Alibaba T-head E902 32-bit RISC-V @ 150MHz

- Memory – 728KB SRAM, 64MB embedded DRAM

- AI accelerator – NPU BLAI-100 (Bouffalo Lab AI engine) for video/audio detection/recognition

- Wireless

- 2.4 GHz 802.11 b/g/n Wi-Fi 4

- Bluetooth 5.x dual mode (classic + BLE)

- IEEE 802.15.4 for Zigbee

- 10/100M Ethernet through add-on board

- Display

- Up to 4-lane MIPI DSI

- Up to 8-bit MIPI DBI

- 16-bit MIPI DPI

- QSPI

- Audio Codec – 2x ADC, 1x DAC, sample rate: 8 to 192KHz, 24-bit

- Camera

- 2-lane MIPI CSI and DVP interfaces

- MJPEG and H.264 encoder up to 1920×1080 @ 30fps + 640×480 @ 30fps

- Package – 88-pin QFN

- CPU

- Storage

- 16Mbit (2MB) or 128Mbit (16MB) XSPI NOR flash

- MicroSD socket with support for SDHC and SDXC

- Camera & audio – 2-lane MIPI CSI co-located with USB-C port for camera module including microphone and speaker

- Antenna – 2.4GHz chip antenna soldered on board, footprint for u.FL connector

- USB – 1x USB 2.0 OTG Type-C port with MIPI CSI “alternative” mode

- Expansion – 2x 20-pin headers with castellated holes with GPIO, SPI, I2C, and UART, possible I2S and GMII expansion

- Debugging – 5-pin JTAG header

- Misc – BOOT button, red power LED

- Power Supply – 5V/0.5A via USB Type-C port or micro USB port

- Dimensions – 51 x 21 x 19mm

There have been several Arm processors with built-in 64MB to 128MB memory from Allwinner and SigmaStar in recent years, so it’s interesting to see Bouffalo Lab doing something similar with the BL808 RISC-V SoC. There are some more details including the Ox64 schematic and BL808 datasheet + TRM in the wiki.

The BL808 wireless processor is designed for low-power AIoT video/audio applications, notably two-way voice intercoms. The BL808 is supported by an RTOS SDK, and Linux is being worked on. That’s why there are two SKUs for the Ox64 board, one with 16Mbit flash suitable to run an RTOS and another one with 128 Mbit flash to run Linux.

Pine64 Ox64 is available for purchase for just $6 for the 16Mb Ox64 and $8 for the 128Mb Ox64. You’ll find both on the Pine64 store. Note that at this early stage, I would not expect all features to work outside of the box.

Update: The post was initially published on October 10, 2022, and updated once the Pine64 Ox64 was up for sale.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress. We also use affiliate links in articles to earn commissions if you make a purchase after clicking on those links.