Microchip recently introduced the PIC16F13145 series of 8-bit MCUs featuring a Configurable Logic Block (CLB). This allows users to create custom hardware-based logic functions within the MCU. This approach lowers the BOM costs and boosts performance.

Last year, we saw Microchip introduce PIC32CZ Arm MCU with a Hardware Security Module (HSM) and before that, we saw they launched LAN8650/LAN8651 10BASE-T1S single-pair Ethernet Controllers. Feel free to check those out if you are interested in the topics.

Microchip PIC16F13145 Series MCU Specification:

- 32MHz PIC16 CPU core

- Up to 1KB User SRAM for application data

- Up to 14KB Flash memory with code protection features

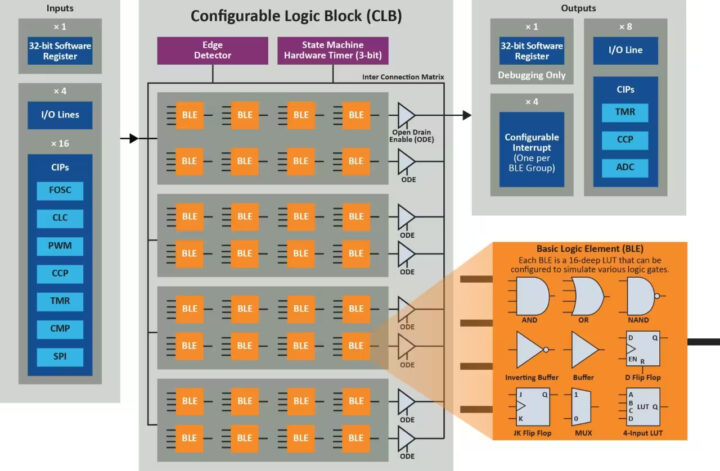

- CLB Capabilities:

- Up to 32 basic logic elements – AND/OR/NAND/NOR gates, buffers/inverting buffers, D/JK flip-flops, multiplexers, 4-input LUT

- Dynamic configuration for on-the-fly changes

- Tri-state logic capability

- Inputs/outputs from software, I/O pins, and PIC® peripherals (ADC, PWM, DAC, etc.)

- Less than 6 ns BLE propagation delay at 5.5V (typical)

- 20 uA per BLE power consumption at 1.8V/1 MHz (typical)

- Configurable boot memory and SAF area for secure data storage

- Device Information Area (DIA) and Device Configuration Information (DCI)

- 32-bit Cyclic Redundancy Check (CRC) with an independent operating memory scanner for data integrity

- 10-bit ADC with computation (300 ksps) and channel grouping for advanced input handling

- 8-bit programmable DAC with two buffered outputs for precise analog output

- Two high-speed comparators for quick response applications

- Fixed Voltage Reference (FVR) and factory-calibrated temperature sensor for accurate measurements

- High-precision internal oscillator (+/- 2% accuracy) with clock switching and support for external crystal oscillators and external clock

- One MSSP module configurable as SPI or I2C (up to 400 KHz) for versatile communication options

- One EUSART with auto baud for serial communication

- Three timers (combination of 8- and 16-bit) with hardware limit features for precise timing control

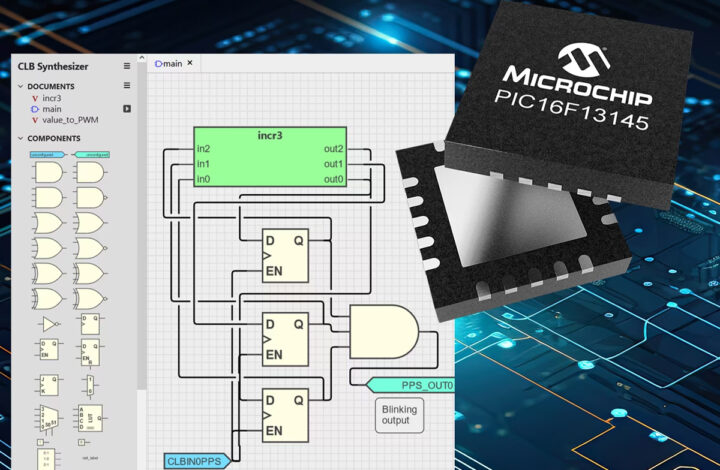

- MPLAB Code Configurator (MCC) supports easy GUI-based peripheral and function configuration, including a specialized CLB graphical interface for dynamic logic design

The MCU family features 8, 14, and 20-pin controllers, with up to 14 KB flash memory and 1 KB RAM. It includes a 10-bit ADC (up to 100 ksps), an 8-bit DAC, fast comparators (50-ns), and peripherals for timing and serial communications, including SMBus support.

Customizable Logic is similar to what you find in programmable logic devices (PLDs) and it’s the key feature in Microchip’s latest MCUs. With a Configurable Logic Block (CLB) You can program each element to do different logic tasks. These logic blocks use look-up tables (LUTs) to set up either complex or simple logic functions, like AND, OR, and XOR gates. Engineers can use these LUTs to design custom circuits right inside the MCU, working separately from the main CPU. This approach not only reduces the bill of materials (BOM) costs but also reduces power consumption. More information on CLBs can be found in the online documentation.

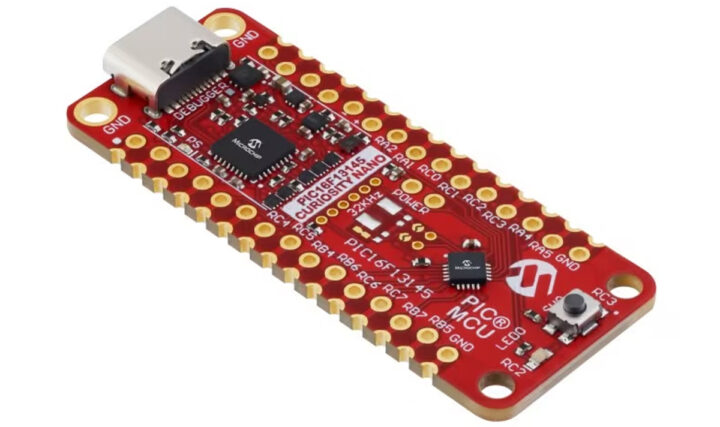

For those who are interested in getting started with Microchip PIC16F13145 Series MCU, Microchip recommends the PIC16F13145 Curiosity Nano Evaluation Kit. They also offer a getting started guide and sample codes to help you kick off your projects.

More information about the PIC16F13145 MCU family can be found on their product page. You can also find this microcontroller on Microchipdirect and DigiKey.

Debashis Das is a technical content writer and embedded engineer with over five years of experience in the industry. With expertise in Embedded C, PCB Design, and SEO optimization, he effectively blends difficult technical topics with clear communication

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

I like the idea of this, but keeping track of what logic of in hardware and what isn’t seems like a hassle in the long run.

I guess you could implement a sort of safety-related block using this –

Let’s say portb.1 and portb.2 have inverted logic input, then

(portb.1 == portb.2) is illegal and must put the system in a safe state.

Having the logic in hardware could be considered safer than in software, and thus easier to certify.

Can you call a function directly, or do you need to set an (internal) hardware pin?

In Aviation fpga and cpld are considered complex equipment and need an extra level of certification as compared to software.

But Boeing can build some new Mcas with this pic and classify it level e SW 😛

PIC? In 2024? They have ARM licenses for the latest cores, why saddle them with a dead-end arch?

Everything doesn’t have to be arm.

Also, it may be easier to integrate their own IP’s, instead of using this (relatively old) ip with ARM.

That license is not all-you-can-eat. Arm charges them per device shipped.

> 32-bit Cyclic Redundancy Check (CRC) with an independent operating memory scanner for data integrity

What’s this, exactly? Some kind of poor man’s ECC?