It’s official, there’s a bubble of Rockchip RK3399 boards announcements or launches in early 2018. After AAEON RICO-3399, Orange Pi RK3399, and Pine64 RockPro64, which add to 96Boards compliant Rock960 announced a couple a months ago, and which may launch in Q1 2018, Hardkernel has now announced they’ve been working on ODROID-N1 board.

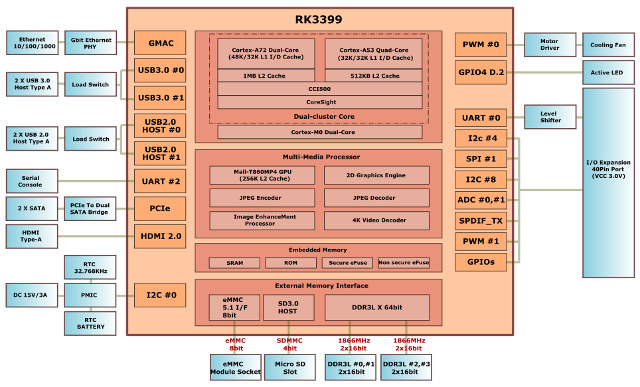

ODROID-N1 board specifications:

- SoC – Rockchip RK3399 hexa-core processor with a dual-core Arm Cortex-A72 @ 2GHz, a quad-core Arm Cortex-A53 @ 1.5Ghz, and a Mali-T860MP4 GPU that supports OpenGL ES1.1/2.0/3.0, OpenCL 1.2

- System Memory 4Gbyte DDR3-1866 RAM, Dual channel interface for 64bit data bus width

- Storage – eMMC 5.0 (HS400) flash storage, UHS capable micro-SD slot., 2x SATA3 ports using, native SATA implementation via PCIe-gen2 to SATA3 interface

- Video Output – HDMI 2.0 for 4K display

- Connectivity – Gigabit Ethernet port

- USB – 2x USB 3.0 host ports, 2x USB 2.0 host port.

- Expansion – 40-Pin GPIO port with GPIOs, I2C, SPI, S/PDIF, PWM, ADC, UART, GND, 3.0V, and 5.0V

- Power Supply – 12V/2A by default, but adding two 3.5″ HDD will require a 12V/4A PSU

- Dimensions – 90 x 90 x 20 mm (excluding cooler)

The company will officially support Ubuntu 18.04 or Debian Stretch with Kernel 4.4 LTS, and Android 7.1. Linux 4.14 has also been found to be working, except for some GPU/VPU issues, so a kernel update is possible/likely.

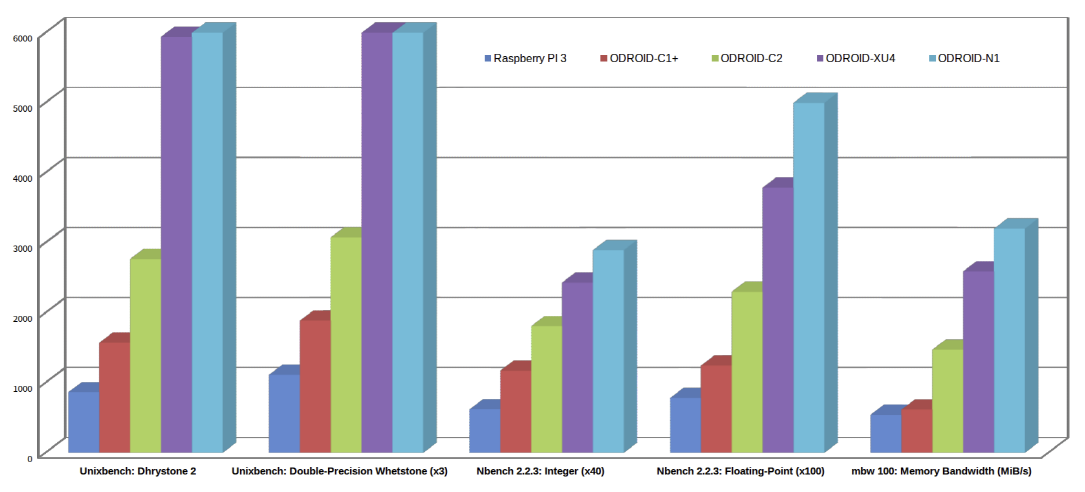

Beside the specifications, it’s also interesting to learn why they made the board: as an upgrade to ODROID-XU4 / XU4Q (which will still be mass-produced). The company also looked at Amlogic S912 and Realtek RTD1295, but decided Rockchip RK3399 was the best match for the requirements of their community. Compared to ODROID-XU4, ODROID-N1 will come with a faster CPU & GPU, more DRAM memory, faster storage IO, and be more Linux friendly.

As with the ODROID-XU4 family there will be an actively cooled model, and a passively cooled one with a bigger heatsink. The latter will work well for most people, but if you need to continuously run loads using all 6 cores at full power, the former will perform a bit better overtime.

What may be disappointing if that we’d have to wait a few more months before availability. The company will send 30 engineering samples to pre-selected members of the community for a “Debug Party” to further test the board before mass production, expected in May or June. Price should be around $110, with the final price depending on the DRAM market price. If the board is popular, an ODROID-N1 Lite version with 2GB RAM and no SATA port may be launched later on for $75.

Thanks to Jerome, T, crashoverride, and Nanik for the tip.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress. We also use affiliate links in articles to earn commissions if you make a purchase after clicking on those links.

Unixbench and NBench scores in 2018. Close to unbelievable. 🙂

By looking at the picture it seems they use an ASM1061 for SATA which would be very disappointing given that an ASM1062 would at least use 2 PCIe lanes instead of one. And I’m already curious how funny IO performance differences later will look like comparing those OS images that don’t care about important stuff (eg. IRQ and SMP affinitiy) and those wo do (with this big.LITTLE SoC some of this settings stuff will be a bit challenging).

@cnxsoft:

’12V/2A by default, but adding two 3.5″ HDD will require a 12V/4A PSU’ is copy&paste from their announcement but conflicts with the silkscreening on board since there it’s written “15V DCJACK” (which would make more sense to ensure stable 12V are provided to 3.5″ disks).

Besides that this looks well thought (especially disk powering or power circuitry in general) but storage enthusiasts wanting to attach as much SATA disks to a RK3399 device still are better served by RockPro64 (open-ended x4 full size PCIe slot ready to take whatever PCIe card is inserted) or the soon to be announced next RK3399 device from China exposing all 4 PCIe lanes on a M.2 key M connector.

Oh, Hardkernel even explained they use just a single lane ASM1061. And then they elaborate on their tests: ‘When we ran the IOZONE test with a SSD, we could get around 380MB/sec with Gen2 mode even though we expected more than 450MB/sec.’

You will run here into the same 400 MB/s limitation as with USB3/UAS since you’re bottlenecked two times by inefficient/old 8b10b encoding. PCIe 2.x uses 8b10b as SATA does: eight bits of data are transmitted as a 10-bit entity called a symbol, or character (quoting Wikipedia 😉 ). So you waste 20% between SoC and SATA controller and another 20% between controller and disk. ‘5Gbps here and 6Gbps there = 5Gbps bottleneck’ doesn’t apply 🙂

But the way more interesting question is how random IO will look like with SSDs and there the PCIe solution should easily outperform USB3 with appropriate settings (with stupid IRQ/SMP affinity settings there might be even no big difference at all if everything collides on cpu0).

And don’t know how much ASM1061 and ASM1062 differ in price but choosing the latter on such a board seems obvious to me (not only then ~450MB/s are possible but power users wanting to connect 2 SSDs are also much better served since bottlenecked with single lane attached controller already)

This is quite a nice announcement. I will watch it closely and I hope the price will be around 100 USD. I am very curious if it can boot from SATA ports and if eMMC will come preinstalled or configurable as it was with all their oDroids so far.

@tkaiser You are a member of the Hardkernel forum, why not join in the discussion there to voice your concerns or questions?

Now that Hardkernel also joins the ‘SPI NOR flash on board’ club as soon as they manage to throw a bootloader in there with drivers for PCIe and their ASMedia controller this could be possible. With bootable SPI flash combined with pretty fast SATA or USB3 storage there’s also no need for any SD cards or the eMMC any more. I just hope they replace ASM1061 with ASM1062 for obvious reasons…

Unless it has SPI, it will not.

ODROID-XU4 vs ODROID-N1

4 big cores vs 2 big cores

so new board has less CPU power 🙁

@Mihai

If you take a look on the Firefly Boards. It will propably around 100 – 150.

Just been reading today’s Intel post on your site CNX and seem to me there is a market for a very low power, high efficiency, cooler design, for premium ARM boards going forward.

Maybe I am wrong, but in the SBC and TV box space, some seem Keen to have their device run at maximum GHz more of the time, than DVFS allows.

@tkaiser You are a member of the Hardkernel forum, why not join in the discussion there to voice your concerns or questions?

@Philipp Blum

The Firefly board is $150 for a 2GB board. The Odroid N1 is a *4GB* board which Firefly lists for $200.

Huh? This depends on the use case (with a build farm or certain types of pseudo number crunching with inefficient software you might be right).

And we should keep in mind that Hardkernel throws stupid numbers at us. Unixbench is something that was somewhat useful when it was invented over 30 years ago. But it’s not a hardware but just a compiler benchmark in the meantime and just as it is the case with crappy sysbench you can not compare different CPU architectures with such inappropriate tools since they generate only numbers without meaning: http://www.brendangregg.com/blog/2014-05-02/compilers-love-messing-with-benchmarks.html

Beside the blog post linked in the article, they’ve posted it in their forums @ https://forum.odroid.com/viewtopic.php?t=29932

So feedback can be left there too.

This is going to be an interesting year for RK3399 🙂 …

To get lost between ‘it’s too expensive!’ — ‘no, it’s not!’ absurdity? 😉

The only interesting question around RK3399 (at least for me) is how PCIe performance looks like and which potential bottlenecks exist inside the SoC since everything else is long known (and that’s a real problem with those vendor communities since they don’t get that RK3399 here is the same as RK3399 there and that if you know how a chip from the same SoC familiy like RK3328 sharing the same hardware block behaves you know almost all wrt the other SoC in the same area).

And this question (overall PCIe performance) can obviously not be answered by Hardkernel if they already wasted 3 PCIe lanes on their current design. Fortunaly @ayufan brought a RockPro64 board with him from FOSDEM and thankfully TL Lim from Pine Inc. donated a very fast Samsung 960 Pro NVMe SSD. So once ayufan got the board up and running and I get SSH access I could answer this question myself. 🙂

@tkaiser

I shared the same quandary. Before advocating for a 2 lane SATA bridge, I wanted to know if it made any real world difference. If there is a SoC bottleneck, there may be no significant difference between 1 lane and 2 lane when moving data to/from proc/memory. There is a long history of ARM boards with internal IO bottlenecks in my ARM graveyard.

I look forward to hearing the results of your 4 lane tests.

Over in HK forum Justin explained something wrt PCIe link speeds (the ‘datasheet downgrade’) and by some googling I came accross this: https://patchwork.kernel.org/patch/9345861/

So most probably we’re talking about more than one SoC bottleneck already: per lane link speed saturation issues and most probably also an overall bandwidth/latency bottleneck and maybe one influencing the other (eg. 2 lanes used –> both only negotiating at 2.5GT/s). This gets interesting and I realize that I know close to nothing about the hardware related PCIe aspects yet 🙂

One point to note from Odroid forum, said in in site admin post

” We hope that mass production will begin in May or June if the “Debug Party” is successful.

However, if the N1 board is not affordable, or there are too many unresolved issues then mass production will be delayed. “

Well Odroid state there is a bottle neck in the SoC, on their own tests,

” Two SATA3 storage devices can connect to the N1 board via standard SATA data and power cables. The PCIe host can be configured in Gen1or Gen2 mode.

When we ran the IOZONE test with a SSD, we could get around 380MB/sec with Gen2 mode even though we expected more than 450MB/sec.

We suspect that the SoC internal bus connection has a bottleneck. Further investigation is needed to find any room for improvement.

Despite this, 380MB/sec is not a bad number in the ARM SBC world. ”

” SATA interface performance

There are two native SATA3 ports on the N1 board. The SATA3 interface is implemented using 1 x PCIe link in the RK3399. ”

” Known issues in the engineering sample PCB: ”

– Because the SATA power connector has no 12Volt rail and only 2.5” SSD/HDD storage devices can be used. The 12V rail will be added to the mass production version PCB for 3.5” HDD support.

– The UART port on the 40pin GPIO header doesn’t work due to a missing power line in the level-shifter circuit. We will solder a wire on the PCB to solve this issue which will be corrected on the mass production version.

– A 128Mbit(16MB) SPI flash memory chip will be added if our SPI boot implementation is successful.

– Other unidentified issues likely exist.

We may start to ship the engineering samples early next week and there will be a sub-forum for N1 Debug Party.

The list of community members will be available this Friday.” Odroid site admin.

@theguyuk

It means that, just like with every other company, timelines are subject to change. The difference is that the timeline is public. This is contrast to other companies that cite the “Osborne effect” as reason to never disclose future product plans.

Also of interest related to the Osborne axiom is the forum post that states “We are selling the XU4 board like a hot cake after announcing the N1 board today.”

s/a passively cooled one with a bigger fan/a passively cooled one with a bigger heatsink

I will wait for Hikey 970 or 975

more(2x) big cores, faster( 2,4 vs 2,0 GHz) and better production technology

You should write less and read more (carefully). They wrote they suspect a bottleneck in the SoC since they got a 380 number where they exptected 450. But the 380 MB/s are a pretty normal number for a SATA controller attached to a single PCIe 2.x lane. The numbers I got with both ASM1061 and Marvell 88SE9215 at different PCIe controllers never exceeded 395 MB/s and with ASM1061 the maximum was 390 MB/s. So there’s no reason to assume a ‘SoC bottleneck’ when getting 380 MB/s with the same controller and same topology. Easy to verify by searching the web eg. http://www.tomshardware.de/ssd-motherboard-chipsatz-performance,testberichte-241308-4.html

As a comparison the aforementioned Marvell 88SE9215 when attached to a PCIe 2.x lane of a Marvell Armada 3700 SoC (EspressoBin) scores only 290 MB/s any more which now is a clear indication for a different bottleneck. But in this case it was more of a CPU bottleneck (benchmark processing and PCIe IRQ processing fighting for low CPU ressources) since same SSD tested on the Armada’s native SATA port scored much better (430 MB/s) and increasing CPU clockspeed by 200 MHz also helped with improving both numbers.

So the obvious next tests are looking into link training issues when more than 1 lane is involved (use 2 or more lanes in parallel just to realize that now only 2.5GT/s per lane can be negotiated any more?) and test with all 4 lanes in parallel. If there’s an issue with 2 or more lanes in parallel leading to just 2.5GT/s negotiated link speed that would mean we’re talking not about ’20 Gbps PCIe bandwidth’ but just the half. And that might also explain why Rockchip downgraded the 5GT/s in their datasheet to 2.5GT/s last year.

I hope soon we’ll know a bit more 🙂

@tkaiser

Later in the N1 introduction thread, odroid mentions that there was a change to the manual for the chip saying that there is only Gen1, not Gen2. So, they may need to go with two lanes if the chip (or future revisions) will only support Gen1.

And, of course, you should take a few lessons about good manners 🙂

@tkaiser

You should assume less.

Odroid said ” We suspect that the SoC internal bus connection has a bottleneck. Further investigation is needed to find any room for improvement.

Despite this, 380MB/sec is not a bad number in the ARM SBC world. “.

Suspected or known, they state a bottleneck!.

No, please see above. It has been discussed in depth. Also while Justin (‘odroid’) talks about ‘Gen1’ the datasheet only talks about link rates (5 vs. 2.5 GT/s) while Hardkernel reported they got no problems to establish a 5 GT/s link between SoC and their ASM1061 (so it’s obviously Gen2). The potential problem (SoC not able to saturate a 5 GT/s link and therefore in some situations link training between both PCIe PHYs failing and remaining at 2.5GT/s) is also mentioned above (see the patchwork link).

So we can only specultate why Rockchip ‘downgraded’ link rate specs in their datasheet. Could be related to the aforementioned problem that the SoC is unable to cope with 5 GT/s (dependent on board design and maybe also dependent on count of lanes used in parallel?), could also be that they tested internally and found that overall PCIe bandwidth is that limited that it looks better to ‘downgrade’ specs.

Anyway, just looked into the datasheet again and this time at page 24: they’re writing ‘Compatible with PCI Express Base Specification Revision 2.1’ and ‘Support 2.5GT/s serial data transmission rate per lane per direction’ which is not really conflicting since 5GT/s are optional if I understood correctly. But at least it’s a bit disappointing.

‘PCIe 2.1’ is great since AFAIK PCIe power management was not available before, the link speed ‘downgrade’ is maybe just due to those link training problems or maybe should serve as an indication that overall performance will be limited to 10GT/s. I think we need a few more tests to come to conclusions?

@willmore

One cannot get 380MB/s on a single-lane PCIe 1.x.

@willmore

Xalius threw this link at me: pcisig.com/sites/default/files/files/02_01_Troubleshooting_PCI_Express_Link_Training_and_Protocol_Issues_FROZEN.pdf

Very interesting read and also explains that with PCIe it’s the same mess as with USB. People talk about USB 3.0 and mean 5 Gbps (while this is ‘SuperSpeed’ in reality, there is no direkt ‘link speed’ to ‘protocol revision’ relationship) and the same with PCIe ‘Gen 2’ and 5 GT/s (optional).

I like this board. It’s a good balance of features and price. And with Hardkernel behind, with its excellent track record of well supporting their products, it might quickly become the best supported and most affordable RK3399 board to run Linux. It’s basically the same price as the H96Max but without the hassle 🙂

okay but then what was usb 3.0 designed for, high power devices ?

it’s one thing to say that’s it’s backward compatible with lower speed configurations but when you get a specific hardware revision the obvious expectation is to get the full spec support..

I’m not having an argument with you, just saying that we should all expect proper design when a soc or board announces support for a specific “high speed” bus.. and not downgrade our expectations.

i’m not quite on board (pun intended) with you, at 100$ (and even well below that actually) you enter the x86 intel boxes (boards ?) domain, most of them already supporting high speed buses of various kinds, sata, mpcie, usb 3.0.

i understand that some specifically (network related) designed arm socs/boards with a large number of i/o buses meet some market needs, i’m not sure where arm socs stand in other cases, like with this particular board (at that price at least).

Of course linux getting better and better on many arms socs, it would then not matter much or at all, if you pick an arm or x86 platform..

For me: so close yet so far.

I keep looking for a good Linux board w/2GB RAM and mSATA or M.2 SATA and $75 or less…

(mSATA preferred because minimum cost for 32GB about 1/2 the cost of M.2 SATA.)

@Mike Schinkel

There’s no performance difference between mSATA and ‘M.2 SATA’ since both are just mechanical connectors. It’s just that today you find mSATA ‘SSDs’ (some cheap old NAND dies, wired to some smelly controller that fakes SMART values with a sticker on top to hide the details) for a lower price from questionable sources since currently only quality vendors use the M.2 connector for their products.

Just wait a bit, soon unreliable and slow ‘SSDs’ will also be available with M.2 connector. Oh wait, KingDian is already at it. Look at Jean-Luc’s review a while ago. Maybe only temperature readout via SMART was faked so not that bad 😉

@tkaiser

You’re conflating Gen notation and Version notation. Version refers, as you mention, to the protocol version which determines higher level properties of the signaling as well as various physical parameters–power delivery, etc.. Gen refers to the signaling speed introduced in the corresponding Version. Thus Gen1 means 2.5GT/s, Gen2 means 5GT/s, etc.. Implementations of a Version require all of the protocol support from that Version, but don’t require all of the link speeds to be supported. Hence why we can have Version 2.1 Gen1 ports. This is complicated by embedded PCI-E devices (like the one on this board) because not all of the Version applies as it covers things like slot power delivery, etc..

USB has a similar issue, but they have at least adopted formal names for their different link speeds–Low Speed, Full Speed, High Speed, SuperSpeed, Superspeed+ (and then they messed up by reusing Superspeed+ to mean 20GB/s). This is separate from the USB version in the same sense as PCI-E as an implementation of a Version may support all link speeds up to the one introduced in its Version, but is not required to. This is all complicated as both of these specification families have related specifications (in the case of USB, they have power specs and connector specs) which get incorporated with new Versions, but can be later updated on their own. This leads to confusing things like a Type-C port that is only High Speed.

The HK board just LOOKS better quality than the Rock64 or ORangePi versions which look bodged together

Indeed! Thanks for the correction and the additions!

ODROID N1 sample arrived few hours ago so let’s start to identify the bottlenecks (at least for the use cases I’m interested in 🙂 )

https://forum.armbian.com/topic/6496-odroid-n1-not-a-review-yet/

i wonder how the Odroid-N1 (rk3399) compares to the Latte Panda Delta ( N4100 celeron). Both are similarly priced (120/150). Both have SATA, 4GB RAM e.t.c. The delta comes with integrated WiFi / Bluetooth and an onboard Arduino for hardware interfacing e.t.c. The X86 atchitecture also means that in theory at least, the mainline kernel will support the SOC indefinitely

@halherta

The RK3399 when running things on one of the A72 cores should still be slightly faster than compared to single threaded loads on the N4100 (only then able to reach burst frequencies above 2GHz, as soon as more than one CPU core is busy the Celeron has to drastically reduce clockspeeds so most probably with multithreaded workloads the RK3399 will easily outperform the Celeron).

Wrt expansion options the Lattepandas have twice as much USB3 ports, only one SATA but still at least two PCIe Gen2 lanes available at an M.2 connector (even 6 on the Alpha) so if the user is willing to deal with mechanical adapters expansion possibilities are great. I think all RK3399 devices have a hard time now competing with latest Intel low power designs…

Wrt kernel there shouldn’t be issues with RK3399 since Rockchip guys themselves actively upstream platform support to mainline Linux kernel. I would only be concerned when thinking about the other interesting operating systems besides Linux and Android (*BSD, Solaris and few others)