SiFive Performance P550 was supposed to be the most powerful RISC-V core to date, capable of outperforming Arm’s Cortex-A75 core in raw performance, but especially in terms of efficiency, with three times the performance per mm2.

But there may be an even more powerful RISC-V processor, albeit developed as a research project, with the Chinese Academy of Science (CAS)’s XiangShan open-source processor presented at the recent RISC-V World Conference China 2021 with the goal of matching Cortex-A76 performance.

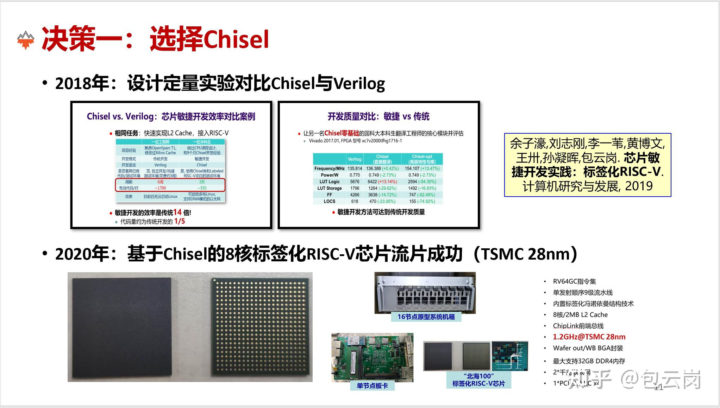

The project was launched on June 11, 2020, and 25 classmates and teachers participated in the development of Xiangshan with 821 main branch code mergers, 3296 code submissions, more than 50,000 lines of code, and more than 400 documents, mostly in Chinese only for now.

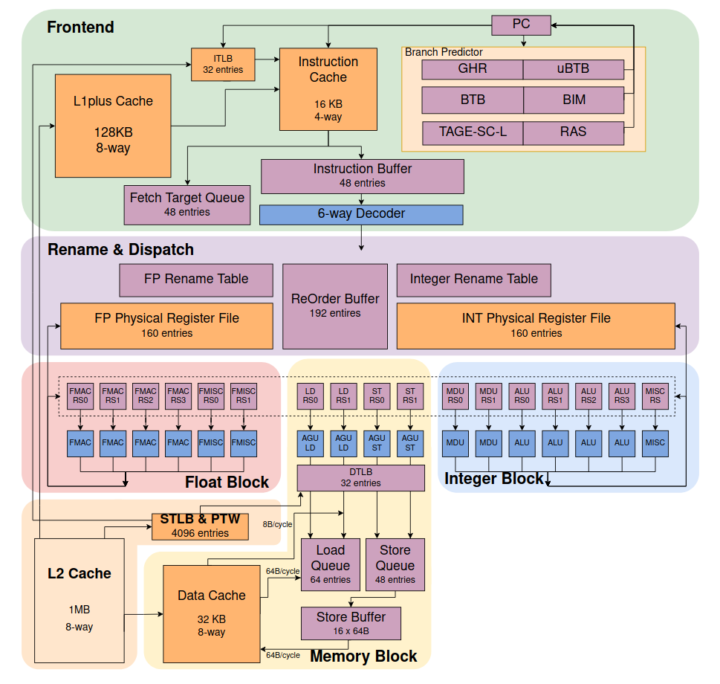

This culminated with an 8-core prototype built based on Yanqihu () architecture using TSMC’s 28nm process with the processor running up to 1.2 or 1.3 GHz that should be taped out this month. But plans have been made to tape out a new prototype based on Nanhu () by the end of the year, using SMIC’s 14nm process allowing up to 2 GHz frequency, and further iterations of the architecture will aim at rivaling Arm’s Cortex-A76 processor.

The current implementation relies on RV64GC RISC-V architecture, includes 2MB cache, PCIe interface, and supports up to 32GB DDR4 memory. The XiangShan processor has been tested with Debian on an FPGA platform, and eventually, it may end up supporting Ubuntu which recently ported to HiFive RISC-V boards.

The RISC-V core has been developed with the Chisel language, which the developers claim requires five times fewer lines of code than Verilog, and much faster to develop with, according to a recent post in Zhihu (in Chinese). You can find the source code released under a Mulan PSL v2 license (Mulan Permissive Software License, Version 2), and some documentation in English and Chinese on Github.

Since it’s a university project, it’s unclear whether it will ever be used commercially, but considering the Chinese government is looking for alternatives to x86 and Arm, I would not be surprised if XiangShan ends up in a processor for the Chinese market.

Via Heise

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

The good old AMD, Cyrix and Intel competition days come to mind. Competition can be good for users ?

The names seem like a play on Intel’s naming scheme. With 湖 meaning “lake”

The license seems “BSD-like”

more info (with links to even more info):

https://issues.apache.org/jira/browse/LEGAL-513

Very cool. I think it makes sense for an educational institution to be involved in this since it’s an open architecture.

Anyone have a sense for what SiFive’s long term game is? The other (Chinese) RISC-V players seem to be shooting for lock-in through things like custom “NPU”-stlye cores. I don’t understand what’s SiFive’s business case. Do they have an big IP portfolio or something?

SiFive’s business case is that they have been working on RISC-V for longer than any other company, and as such they can provide better services. But with this coming out, it makes you wonder if their business case is found, because it seems like general experience in CPU design might be more important than knowing the specifics of RISC-V.

The other (Chinese) RISC-V players seem to be shooting for lock-in through things like custom “NPU”-stlye cores. Compared to traditional ISA, RISC-V’s model the exact opposite of lock-in. RISC-V was designed for the purpose of letting fabless focus on value extensions while leaving the common core instructions generic. If a different player comes along with a superior instruction extension / core, there’s little stopping you from porting to that since most of the compiler’s output will remain the same. Moreover, just like how it went with DSPs, smartphone SoCs and desktops, over time the branch predictors and catch sizes will… Read more »

Intel aside, ARM is a tough cookie, ARM’s advantages are advanced nodes. The marketing isnt comparing advanced node vs 28 nm node, they are comparing 28 nm to 28 nm. And it could just be marketing hype, promises galore at this point, we havent really testable benchmarks. Chinese companies do such things to whip up interest, but like maglev at 100 kph while claiming 600 kph, i’d like to see much firmer reviews and evaluations before buying in.

Not exactly. Yanqihu is where GUCAS (University of the Chinese Academy of Sciences) located in.

I wonder to which degree is this built on work that went into Loongson. The pipeline diagram for the older 3A2000 shows some similarities beyond the parts that any modern OOO RISC core have in common (turn it 90 degrees), though of course the new one is wider.

It seems that if Loonson still had any ties with CAS ICT, they are cutting them with their current IPO, while also moving away from MIPS in their new LoongArch instruction set that can emulate RISC-V and Aarch64 in addition to MIPS and x86..

Yes they look pretty similar, but honestly it’s quite hard to design a superscalar core that doesn’t look like these ones nowadays :-/ However I don’t yet buy the “it would be faster than A76 if it would run at the same frequency” stuff until that’s done. Plenty of cores are limited to low frequency by design and need to be pipelined differently to achieve higher frequencies, or they’ll have to suffer multi-cycle instructions. If this one ends up maxing out at 2 GHz while A76 reaches 3 GHz with roughly the same IPC, in the end A76 will still… Read more »

Can they over clock the CPU to Hell and put a huge heatsink on top. The same way the Toaster marketed as RPI 4 does.

Can’t wait to see plethora of TV boxes running on these

I was thinking headless servers.

A tv box requires additional IP blocks such as a graphics core. If it is a choice between open source Mali and binary blob PowerVR, I’d stick with ARM!

Vivante?

🙂 Open Source, so I guess any fabricator could use the design.

Kinda takes the wind out of the sales of Intel/SiFive’s recent lovin’…

“wind out of the sales” … nice typo!

A successful go-to market is not only about having chip. It’s about production, logistics, channels, sales (!), support, capital, reliability. Intel could bring that (if they want)

I’m very embarrassed by the homophone error. I couldn’t seem to edit the entry after I posted and realized my faux pas. :/ But I guess it is about eventual sales.

Lee Matthews, over at Liliputing, suggests that “the Chinese government has been actively seeking alternatives to x86 and ARM for quite some time.” My guess is that they’ll be eager to see these designs implemented.

As for me… I’d far rather go for an Open Source chip. And it looks to be more powerful than SiFive’s P550 too. I hope it’s widely utilized, and made available internationally.

As said in the article, they are just produced in 28nm ASIC this month and the second version in 14nm this fall. Don’t forget the Chinese domestic market is the biggest in world. This allowed them to already go on technology top on so much technologies area (construction, rail, space (station use ionic engine), the world top supercomputer during 5 years). And they will (As European Union does with its own partially RISC-V based processor) probably use it in their own supercomputers to accelerate fundamental/applied research. Sunway cores opened in 2012 the way where power/energy ratio is more important that… Read more »

Yes! Modularity is turning out to be a very important design feature of RISC-V; producing faster and ever more power-efficient cores. And I agree, it does seem that the world is turning very decisively towards RISC.

What’s interesting (to me) is that this is the second open source RISC-V academic-institute-led initiative… With IIT’s Shakti processor too. The Berkeley Four’s real achievement might be in the demystification of chip design: the proprietary paradigm is at risk from RISC.

Open source chip isnt a big deal as it looks to software peeps. The entire silicon production chain is closed, so opening a single pinhole isnt going to cause Mt St Helens to blow its top off. I see it as a marketing gimmick at this point, something that ARM could copy if it is ever in danger of serious revenue erosion.

Open source chips (and especially the extensibility of the RISC-V ISA, and the design freedom afforded to users of it) is a huge deal, which has already caused Arm to have to rethink their business practice. According to Geng Bo (deputy secretary-general of the China Solid State Lighting Alliance): “It’s said that Arm had cancelled license fees for the companies with financing amount lower than $5 million, to compete with its opponent RISC-V on the aspects of pricing,” And Arm themselves have said on more than one occasion that they are looking at developing Edge technologies, presumably because RISC-V has… Read more »

I’d believe in a heartbeat they built an A76-class multicore cpu. What I don’t believe for a second is that they also built & figured out how to fab a PCIe controller on the same chip. Please, let me be wrong.

If I understand correctly (the relevant line in the picture is covered by the watermark), it’s just PCIe 2.0 x4. It’s not a particularly demanding standard. Every fab and their dog have old PCIe 2.0 IPs that are now irrelevant and these fabs are more than happy to license old IPs to you for free, as long as you build your CPU / microcontroller / whatever with them.

ChiCom hardware? Can you say security backdoors added by ChiCom military? Only fools go there.

As opposed to what? AmeriFree hardware?

While open source security backdoors would require an old switcharoo (potential) or a western trusted fab to be sneaky (unlikely), these processors probably are susceptible to side channel, branch prediction, caching attacks. Why? Because most are, and RISC-V is a very elementary stage and their focus is performance and marketability, and the latter is a more mature stage. Even Intel knew about these flaws for 20-30 years, without acting upon it. Not that they mattered for those decades…

Looks to me like more powerful than P550. Good it’s open source, although I don’t know mandarin so I cannot check their whole license text. Cool!

The license is in English and Chinese. You can scroll down to read the English version.

Legally, the Chinese version is probably enforceable in court and the English translation not. So its not so simple as it looks.

XiangShan is the name of the mountain in northwest beijing.