SiFive has been busy. Just a few days after SiFive Performance P650 announcement, the company has announced the SiFive Essential 6-Series RISC-V processor family starting with four 64-bit/32-bit real-time core, and two Linux capable application cores, plus the SiFive 21G3 release with various improvements to existing families.

SiFive Essential 6-Series range of RISC-V processors

There Essential 6-Seris family is comprised of three sub-families with two processors each:

- E6 Series with 1.91 DMIPS/MHz, 3.69 CoreMark/MHz

- E61-MC – Quad-core 32-bit embedded processor

- E61 – Mid-range performance 32-bit embedded processor (one-core)

- S6 Series with 2.07 DMIPS/MHz, 3.73 CoreMark/MHz

- S61-MC – Quad-core 64-bit embedded processor

- S61 – Mid-range performance 64-bit embedded processor (one-core)

- U6 Series with 2.07 DMIPS/MHz, 3.73 CoreMark/MHz

- U64-MC – Quad-core 64-bit application processor

- U64 – Mid-range performance Linux-capable processor (one-core)

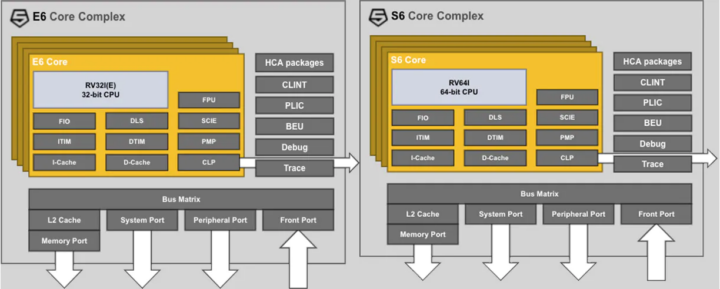

E6-Series and S6 Series real-time processors have practically the same features except for the 32-bit and 64-bit cores, and a different number of interrupts.

- Fully compliant with the RISC-V ISA specification

- Up to four 32-bit RV32I (E6 Series) or 64-bit RV64I (S6 Series) RISC-V cores

- Machine and User Mode Support

- In-order, single issue, 8-stage pipeline

- Advanced Memory Subsystem

- 16KB, 2-way Instruction Cache

- Instruction Tightly Integrated Memory (ITIM) option

- Up to 64KB Data Tightly Integrated Memory (DTIM) support

- Efficient and Flexible Interrupts

- Local interrupts w/ vectored addresses – up to 16

- Platform Level Interrupt Controller (PLIC)

- E6 Series – 128 interrupts w/ 7 priority levels

- S6 Series – 511 interrupts w/ 7 priority levels

- RISC-V Core Local Interruptor (CLINT) – 1 timer, 1 SW

- 8-Region Physical Memory Protection (PMP)

- High-performance AMBA Interfaces

- Detailed Power, Performance, and Area (PPA) Information – SiFive will only tell you by email…

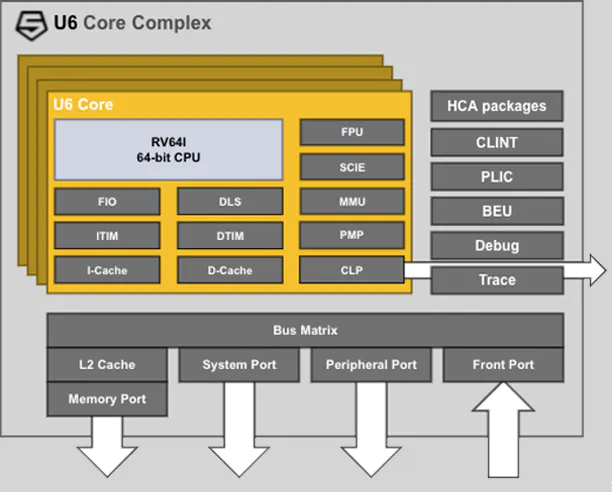

U6 Series application processors highlights:

- Fully compliant with the RISC-V ISA specification

- Up to four 64-bit RISC-V application cores

- 32KB L1 I-cache with ECC

- 32KB L1 D-cache with ECC

- 8 Region Physical Memory Protection

- Virtual Memory support with up to 47 Physical Address bits

- Integrated 128KB L2 Cache with ECC

- Real-time capabilities

- The L2 Cache can be configured into high-speed deterministic SRAMs

- CLINT for multi-core timer and software interrupts

- PLIC with support for up to 128 interrupts with 7 priority levels – Debug with instruction trace

- Detailed Power, Performance, and Area (PPA) Information – Again, tough luck unless you contact SiFive directly

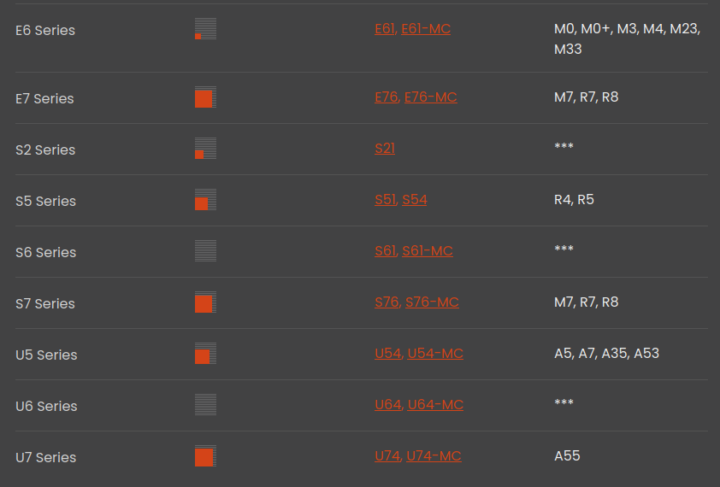

The Essential 6-Series is basically the mid-range equivalent of the high-end SiFive 7 Series processors. Additional details may be found on SiFive Essential page.

SiFive says the E6 Series is equivalent to Arm Cortex-M0, M0+, M3, M4, M23, and M33 cores, quite a wide range, but they did not list any Arm Cortex equivalent for the S6 and U6 series.

SiFive 21G3 release

Besides the new RISC-V cores, SiFive also announced the 21G3 Release with improved clock gating and power management, SiFive Shield WorldGuard support to the Essential family, and the SiFive Performance family now features the RISC-V Hypervisor extension, as noted in the recent announcement of the Performance P650 core. The SiFive Intelligence Extensions as found in the SiFive Intelligence X280, add supports for BFLOAT16 compute, quantization acceleration, and get better multi-cluster support to improve the performance of machine learning workloads.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

I read all that, but it really looks like SiFive is trying to compete with Intel on their horrible naming conventions. I still don’t know what of those chips I can run Linux on and how many actual useful processors it would see and how many of the processors are just little real time coprocessors. What a mess.

I agree, it’s a mess and a pity. They do that on purpose so that we’re completely lost and buy what we don’t need ?

Anyway, the RISC-V center has definitely moved from US to China. And SiFive is less and less relevant.

I’ve read the presse release, and I still don’t understand what “SiFive 21G3” means.

“21G3” – 21 is the short year – (20)21, and G3 is something like “general release 3” I guess.

So 21G3 is not a specific processor/product – it is a version/release with possible minor updates to multiple of their products (IP).