Renesas has recently announced its first homegrown 32-bit RISC-V CPU core based on the open-standard instruction set architecture (ISA). This CPU core is compatible with Renesas’ e2 studio IDE and supports other third-party IDEs for RISC-V MCUs. According to Renesas, the CPU achieved a remarkable 3.27 CoreMark/MHz performance outperforming similar RISC-V architectures in this category.

RISC-V, an open ISA, is rapidly gaining popularity in the semiconductor industry. Many MCU providers have formed joint investment alliances to expedite their RISC-V product development. Previously, Renesas released two CPUs developed by Andes Technology Corp: the R9A02G020, an ASSP EASY MCU for Motor Control, and the R9A06G150, an ASSP EASY MCU for Voice HMI, both based on RISC-V. Additionally, they have introduced the RZ/Five, a Linux-capable 64-bit RISC-V microprocessor family, and RH850/U2B, an automotive System on Chip (SoC). However, with the release of their new CPU, Renesas independently enters the RISC-V market, highlighting their efforts to grow their RISC-V product range.

Key Technical Specifications:

- Versatile Applications: The new CPU is flexible, so it can be configured as a primary application controller, a secondary core in System on Chips (SoCs), on-chip subsystems, or in deeply embedded Application-Specific Standard Products (ASSPs).

- Optimized Performance: The CPU offers optimized performance with options for RV32 ‘I’ or ‘E’, which means it can adjust the number of general-purpose registers to suit the needs of different applications.

- Integrated RISC-V Extensions:

- M Extension: Enhances multiplication and division operations.

- A Extension: supports atomic access, crucial for concurrency in RTOS-based systems.

- C Extension: Offers 16-bit compressed instructions for memory space efficiency.

- B Extension: Provides advanced bit manipulation capabilities.

- Computational Throughput: The CPU delivers 3.27 CoreMark/MHz, outperforming similar architectures in efficiency and speed.

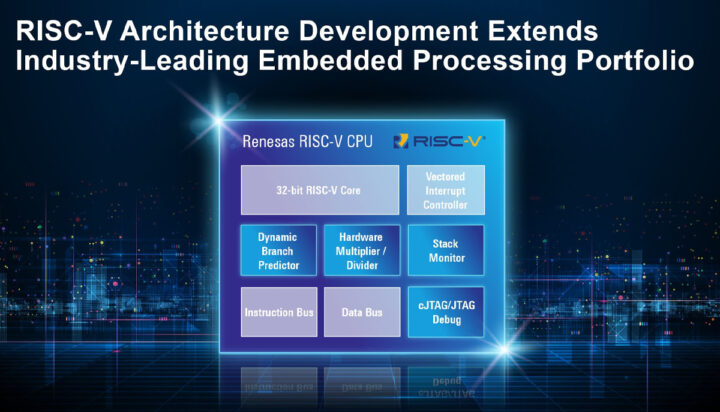

Enhanced Features for Robust Applications:

- Stack Monitor Register: Prevents stack memory overflows, enhancing system integrity.

- Dynamic Branch Prediction Unit: Improves code execution throughput.

- Compact JTAG Debug Interface: Enables efficient debugging, complemented by performance monitor registers.

- Instruction Tracing Unit: offers developers deeper insights into system behavior.

The new CPU is compatible with Renesas e2 studio Renesas e2 studio and a variety of third-party Integrated Development Environments (IDEs), providing a full set of tools for product development. Additionally, the CPU’s features and performance have been verified in a real silicon product, with more details to be released on the EEMBC website after the first product launch in early 2024.

More information on this topic can be found on their product announcement page, while a separate page provides details about the RISC-V CPU core and its features.

Debashis Das is a technical content writer and embedded engineer with over five years of experience in the industry. With expertise in Embedded C, PCB Design, and SEO optimization, he effectively blends difficult technical topics with clear communication

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

I associate Renesas with industrial equipments, automotive, etc. I see this as a big pledge of support for RiscV.

RiscV is getting spicier day by day. Just today, I watched an LTT video about RISC-V pop up on my YouTube homepage.

I’m somehow lost… despite all the marketing around this (great!) news… this architecture has no identifiable name ? Nor the core ? Nor the cpu itself ? “Renesas last risc-v architecture” is how we are supposed to call it.. ?

That’s supposed to be the case for right now! I did a lot of research around while writing but I can’t find any specific name. could be a marketing strategy to keep the hype going.

Strange if they focus on a performance core they didn’t make it 64bit

‘Performance’? This is an MCU and if you believe in CoreMark/MHz then this is for you: https://www.eembc.org/coremark/scores.php (sort by CoreMark/MHz and realize that today’s microcontrollers are as capable as Desktop CPUs from 15 years ago… only ‘per MHz’ of course).

As for 32-bit vs. 64-bit: if it’s the same as on ARM then a 64-bit userland might consume almost twice as much memory w/o apparent performance gains.

I’ve been here long enough to predict the CoreMark comment was coming. 🙂

It doesn’t sound extremely out of proportion, it is somewhere between a Microchip PIC32MZ2048ECH100 and an STMicroelectronics STM32L476

So spot-on for the intended use case…

No point comparing with core 2 duo or athlon xp.