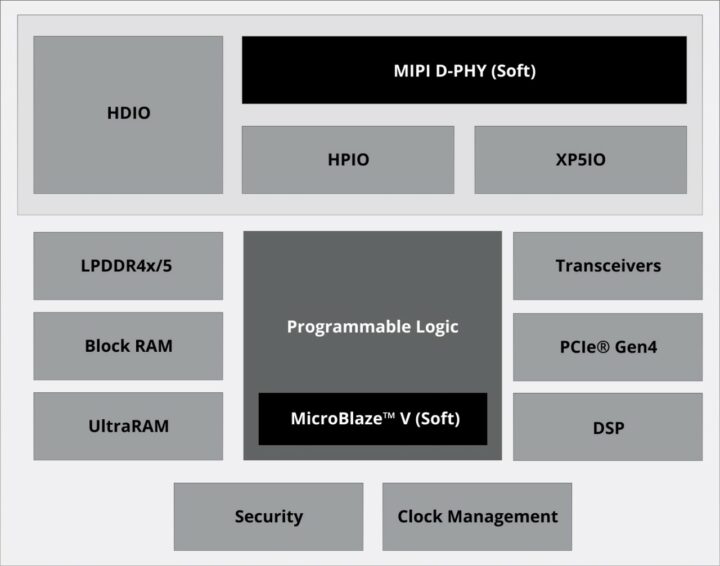

The Spartan UltraScale+ FPGA family is the latest inclusion to AMD’s Cost-Optimized portfolio, a series of FPGAs designed to balance cost, power, and form factor with affordability. The UltraScale+ FPGA family is designed for cost-sensitive, low-power applications requiring high I/O count and substantial security.

Devices in the Spartan UltraScale+ family offer a high I/O to logic cell ratio for FPGAs built in 28nm and lower process technology (the highest in the industry, according to AMD), consume up to 30% less power than compared to the previous generation, and feature robust security features that outclass the rest of the Cost-Optimized portfolio.

This FPGA family is built on the same UltraScale+ architecture as previous Artix and Zynq products. They are the first AMD UltraScale+ FPGAs to feature a hardened DDR memory controller and PCIe Gen4 x8 support, “providing both power efficiency and future-ready capabilities for customers.”

AMD Spartan UltraScale+ specifications:

- System Logic Cells – Up to 218K

- Memory

- On-Chip Memory: Block RAM for low latency, high throughput, and UltraRAM

- External Memory: LPDDR4x and LPDDR5 up to 4266 Mb/s (hard MC), and DDR4 (soft MC) IP up to 2400 Mb/s

- I/O

- I/O Count: 572

- Types:

- High Density I/O (HDIO) up to 3.3V,

- High-Performance I/O (HPIO) up to 1.8V,

- XP5IO up to 1.5V, supporting 3200 Mb/s MIPI and 1800 Mb/s LVDS

- PCIe: Gen4 x8

- Transceivers – Up to 8 GTH transceivers supporting up to 16.3 Gb/s

- Security – NIST-approved post-quantum cryptography, unique device identification, permanent tamper penalty for device protection, and side-attack protection via DPA countermeasures

The Spartan UltraScale+ FPGA series is primarily targeted for embedded vision, healthcare, industrial networking, robotics, and video applications according to the press release. The high I/O count will enable the FPGAs to interface with a wide range of sensors and coupled with the programmable logic make it possible to control the sensors in real time and with low latency.

On the software end, the Spartan UltraScale+ FPGA family (along with the rest of AMD’s FPGA and adaptive SoCs lineup) is supported by AMD’s Vivado Design Suite and Vitis Unified Software Platform. This allows both hardware and software designers to leverage the “productivity benefits of these tools via a single designer cockpit from design to verification.”

AMD Spartan UltraScale+ samples and evaluation kits are expected to be available for sampling and evaluation in the first half of 2025. Documentation is currently available and tools support starting with the AMD Vivado Suite in Q4 2024. To learn more about the Spartan UltraScale+ FPGA family and what it offers, be sure to visit the product page.

Tomisin is a writer specializing in hardware product reviews, comparisons, and explainers. He is very passionate about small form factor and single-board computers.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress. We also use affiliate links in articles to earn commissions if you make a purchase after clicking on those links.