As SiFive has a portfolio of RISC-V cores ranging from low-power E2-series to high-performance U8-series cores with performance similar to Cortex-A7x cores, the company has not released new cores for a while, and instead focuses on improving their current RISC-V cores. We saw that last year with the SiFive 20G1 release that improved performance & efficiency, and lowered the silicon area for the same features set. SiFive further improved its cores and ecosystem with the latest SiFive 21G1 release. The main new features brought by SiFive 21G1 release include: SiFive 2-Series and 7-Series processors are now available with the “Bit Manipulation” extension, RV32B, with Zba and Zbb extensions. This can accelerate Cryptographic Hash algorithms by up to 35% Support for FP16 half-precision floating-point computation in order to reduce memory size and power consumption, and for some AI workloads The memory map is now fully programmable SiFive RV64 processors support up […]

ESP32-C3-DevKitM-1 RISC-V WiFI & BLE board to launch for $8, modules for $1.8+

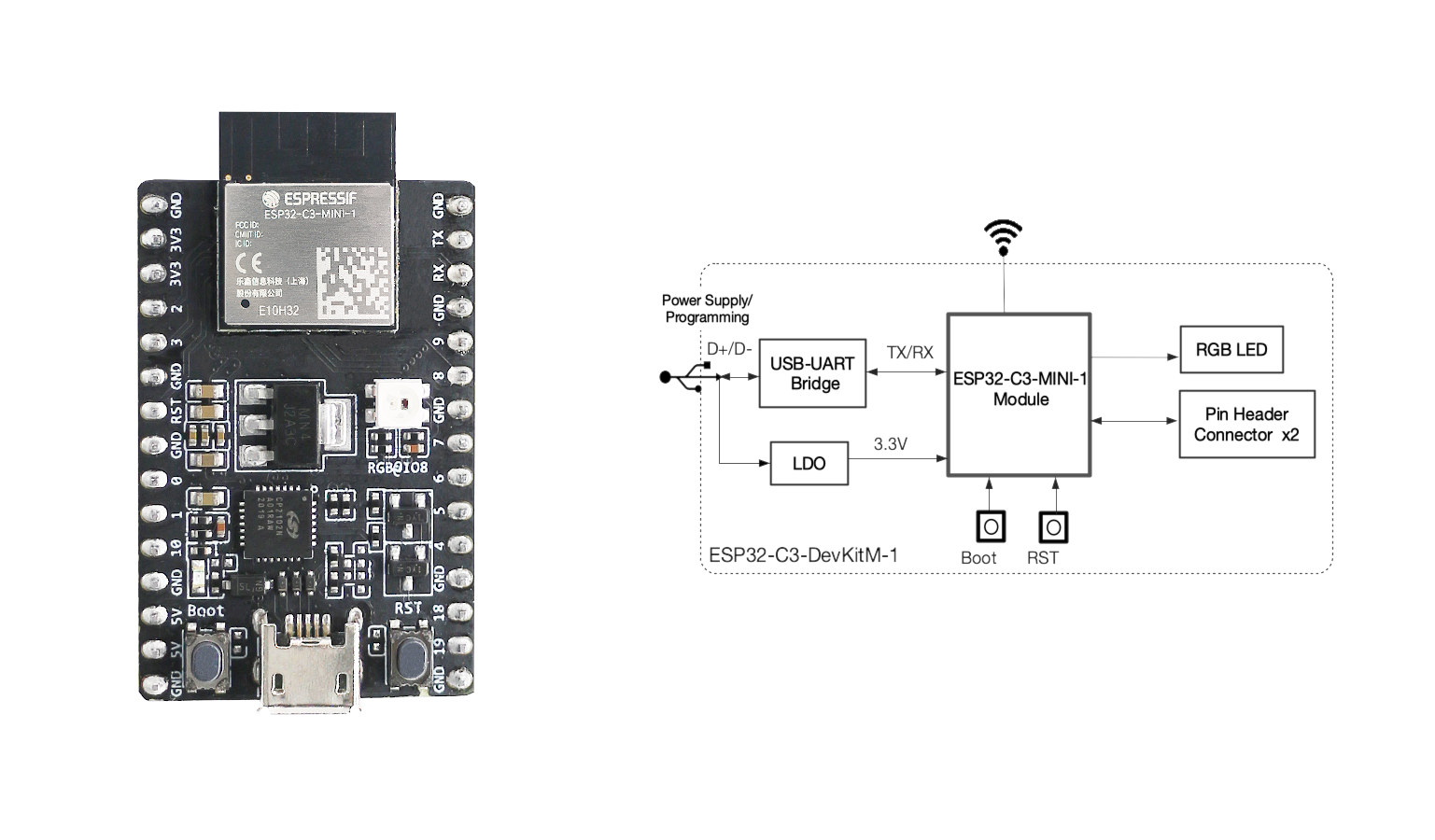

ESP32-C3 may be one of the most expected RISC-V processors in the IoT world, as it’s eventually expected to sell for the same price as ESP8266 and offers both WiFi and Bluetooth LE connectivity. Some engineering samples of the chip. modules and boards were distributed to developers shortly after the announcement at the end of the last year, but now it appears ESP32-C3-DevKitM-1 board will become available for $8 next month from distributors such as Mouser or DigiKey. Since I’ve never written about ESP32-C3-DevKitM-1 board let’s check out the specifications: Wireless module – ESP32-C3-MINI-1 with ESP32-C3FH4 (105°C) or ESP32-C3FN4 (85°C) 32-bit RISC-V single-core processor, up to 160 MHz, 4 MB embedded flash, 384 KB ROM, 400 KB SRAM (16 KB for cache), 8 KB SRAM in RTC Connectivity – 2.4 GHz 802.11b/g/n Wi-Fi 4 & Bluetooth LE 5.0 USB – 1x Micro USB port for power and programming via USB-UART […]

Made in Thailand CorgiDude RISC-V AI board aims to teach machine learning

There’s a relatively small but active maker community in Thailand, and we’ve covered or even reviewed some made in Thailand boards including ESP8266 and ESP32 boards, a 3G Raspberry Pi HAT, and KidBright education platform among others. MakerAsia has developed CorgiDude, a board based on the version of Sipeed M1 RISC-V AI module with built-in WiFi, and part as a kit with a camera and a display used to teach machine learning and artificial intelligence with MicroPython or C/C++ programming. CorgiDude board specifications: AI Wireless Module – Sipeed M1W Module with Kendryte K210 dual-core 64-bit RISC-V RV64IMAFDC CPU @ 400Mhz with FPU, various AI accelerators (KPU, FFT accelerator…), 8MiB on-chip SRAM Espressif ESP8285 single-core 2.4 GHz WiFi 4 SoC plus IPEX antenna connector Storage – MicroSD card slot Camera I/F for 2MP OV2640 sensor up to 1280 × 1024 (SXGA) @ 30 fosm SVGA @ 30 fps, or CIF @ […]

Bluetrum AB32VG1 board features AB5301A Bluetooth RISC-V MCU, runs RT-Thread RTOS

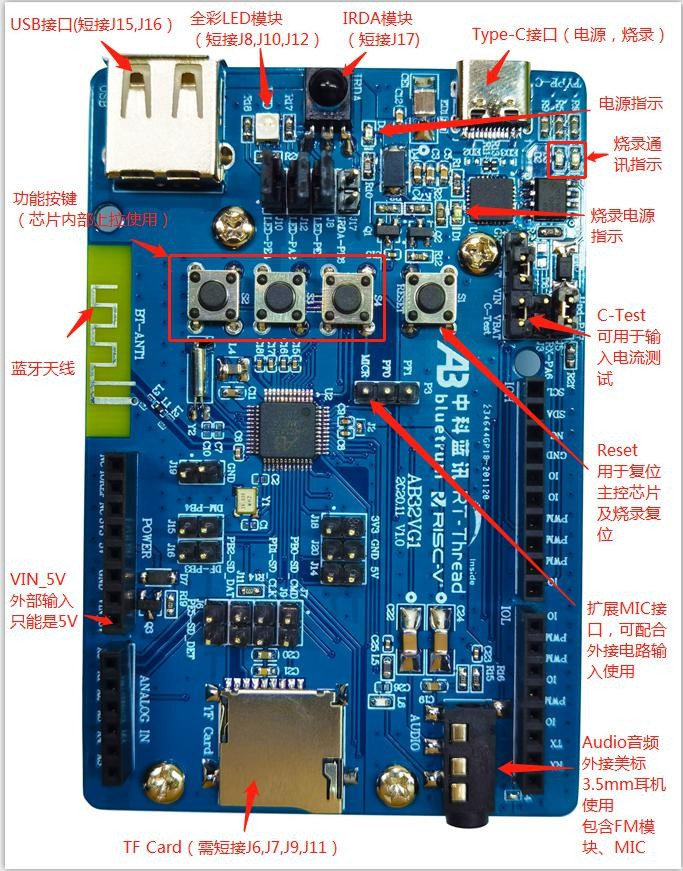

Bluetrum, a Shenzhen-based fabless company focusing on audio chips, has designed the AB32VG1 board based on its AB5301A Bluetooth RISC-V MCU for general-purpose and audio applications. The board comes with a MicroSD card, a USB port, a 3.5mm audio jack, and Arduino UNO compatible headers for easy prototyping. Bluetrum AB32VG1 board preliminary specifications: MCU – Bluetrum AB5301A RISC-V MCU @ 120 MHz (overclockable to 192 MHz) with 192KB RAM, 1MB flash, Bluetooth 5.0 connectivity and FM radio; LQFP48 package Storage – MicroSD card slot Audio – 3.5mm audio jack, 3-pin microphone header Connectivity – Bluetooth 5.0 with PCB antenna USB – USB 2.0 host port, USB Type-C port for power and programming Expansion – Arduino UNO header with 1x I2C, 6x ADC, 6x PWM Misc – IR receiver, 3x user buttons, 1x reset button, RGB LED, power LED, status LEDs, various configuration jumper Power Supply – 5V via USB Type-C […]

ZiHintPause is the first RISC-V extension ratified under the Fast Track Architecture Extension Process

RISC-V open architecture allows designers to implement their own instructions, and some of those may become an official RISC-V extension. But the process to approve a new extension may have been suboptimal, so RISC-V International has just unveiled the Fast Track Architecture Extension Process, or Fast Track for short, that streamlines the ratification of small architecture extensions, as well as ZiHintPause, the first extension to be ratified under the new Fast Track process. The process is designed for simpler extensions that are uncontentious and offer value to the RISC-V community at large, so it’s not suitable for more complex extensions. An extension that has been submitted for consideration will undergo an internal review before entering a 45-day public review process. You can read detailed rules for the new extension ratified process here. The ZiHintPause extension went through this 45-day review process on Google Group, and was very recently ratified. The […]

Linux 5.11 Release – Main Changes, Arm, MIPS & RISC-V Architectures

Linus Torvalds has released Linux 5.11 just in time for… “Valentine’s Day”: Nothing unexpected or particularly scary happened this week, so here we are – with 5.11 tagged and pushed out. In fact, it’s a smaller-than-average set of commits from rc7 to final, which makes me happy. And I already have several pull requests lined up for tomorrow, so we’re all set for the merge window to start. But in the meantime – and yes, I know it’s Valentine’s Day here in the US – maybe give this release a good testing before you go back and play with development kernels. All right? Because I’m sure your SO will understand. Linus Last time around, Linux 5.10 was an LTS release that added EXT-4 performance enhancements, improved post-Spectre performance, as well as the enablement of BCM2711 (Raspberry Pi 4) display pipeline, among other many changes. Some of the notable changes in […]

Ingenic T40 4K Video & AI Vision Processor mixes MIPS & RISC-V cores with AI accelerator

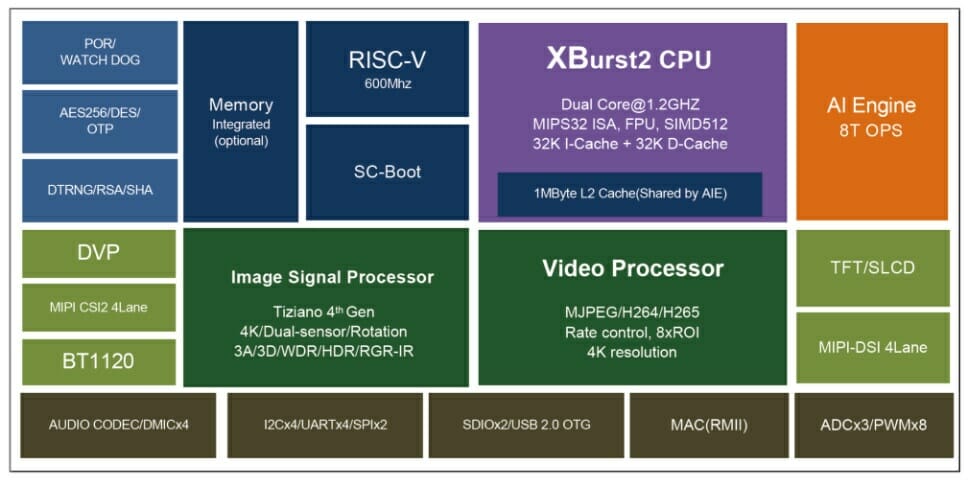

Ingenic T31 MIPS & RISC-V AI video processor was introduced last year with the MIPS core including SIMD128 Vector instructions for deep learning. The Chinese company has now introduced the new Ingenic T40 processor still with MIPS and RISC-V cores, but also a dedicated 8 TOPS AI engine/CNN accelerator. The new processor is especially suited to smart AI vision application thanks to support for 4K cameras, and 4K MJPEG/H.264/H.265 hardware video encoding, complemented by the 8 TOPS AI engine for computer vision workloads such as people detection, face recognition, object detection, and so on. Ingenic T40 key features and specifications: CPU – Dual-core MIPS XBurst2 @ 1.2 GHz with 256KB L2 Cache, SIMD512 instruction set MCU – 600MHz RISC-V coprocessor AI Engine – 8 TOPS neural network accelerator with 1MB memory pool, support for int16/int8/int4/int2 convolution width Memory – DDR2/DDR3/DDR3L up to 2GB Storage – SPI NOR flash, SPI NAND flash, […]

FOSDEM 2021 Online February 6-7 – Hardware, Embedded & IoT talks

FOSDEM is an open-source developer event that takes place on the first week-end of February every year in Brussels, Belgium. Every year except this year, as due to COVID-19 restrictions, FOSDEM 2021 will take place online like most events these days. The schedule has been up for some time, and today I’ll look at some of the interesting talks mostly from the Embedded, Mobile and Automotive “virtual devroom” but also other tracks. Saturday, February 6, 2021 13:00 – 14:00 – From Reset Vector to Kernel – Navigating the ARM Matryoshka Long gone are the times of executing the OS in-place from memory-mapped flash upon reset. A modern SoC now comes with complex mask ROM firmware, with driver, filesystem, protocol and crypto support for loading… yet another bootloader. In his talk, Ahmad follows this chain of bootloaders until the kernel is started, stopping along the way for RAM setup, peripherial initialization, […]