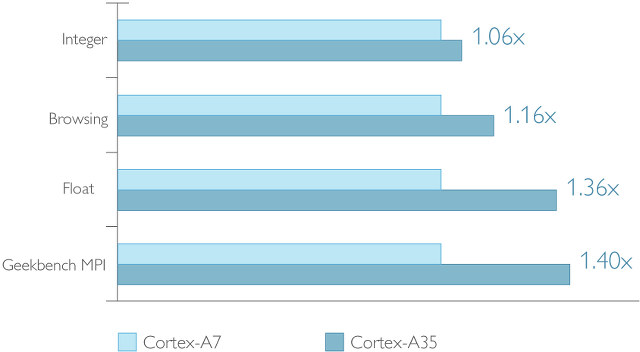

ARM TechCon 2015 has just started, and there have been a few announcements including the launch of a Cortex-A7 replacement with Cortex A35 providing 10% lower power consumption, 6 to 40% performance boost, and a better design flexibility making it suitable for SoC for smartphones to wearables.

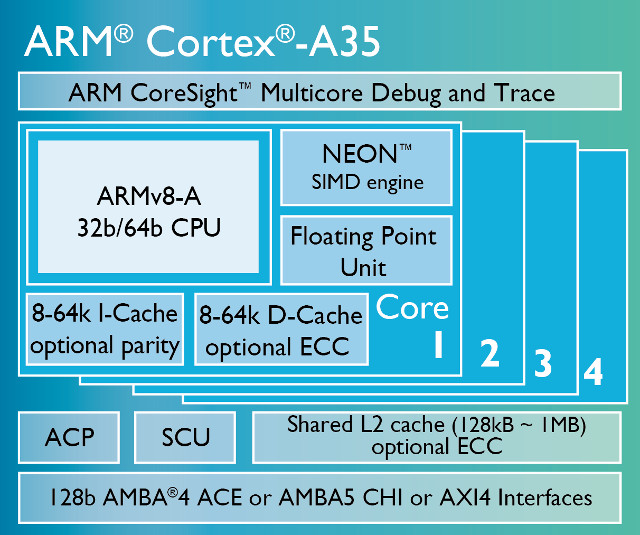

The main specifications of Cortex A35 cores:

- Architecture ARMv8-A (AArch32 and AArch64 )

- Multicore 1-4x SMP within a single processor cluster, and multiple coherent SMP processor clusters through AMBA 5 CHI or AMBA 4 ACE technology

- ISA Support

- AArch32 for full backward compatibility with ARMv7

- AArch64 for 64-bit support and new architectural features

- TrustZone security technology

- NEON Advanced SIMD

- DSP & SIMD extensions

- VFPv4 Floating point

- Hardware virtualization support

- Debug & Trace CoreSight DK-A35

The new core can both be used in quad core configuration at 1 GHz for a smartphone (90 mW per core), or in single core configuration at 100 MHz for wearables (6 mW) in a 0.4mm2 silicon footprint.

Cortex-A35 also consumes about 33 percent less power per core, and occupies 25 percent less silicon area compared to Cortex-A53. Considering quad core Cortex A53 devices ship for less than $50 today, you can expect ultra low cost (and low power) smartphones, wearables, and set-top boxes by the end of 2016. Cortex A35 is also expecting in low-power servers and smart TVs.

Visit ARM Cortex A35 page for more details.

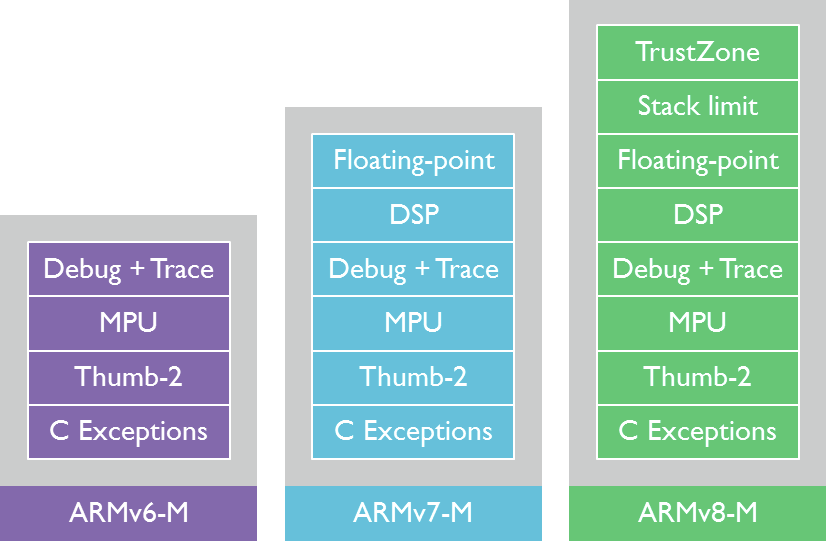

ARM is also addressing IoT security by bringing ARM TrustZone and stack limits to micro-controllers with ARMv8-M architecture.

Some of the key features of ARMv8-M include (new in bold):

- 32-bit architecture

- ARM Thumb-2 technology for excellent code density

- ‘C’ friendly exception model

- Protected memory system support for real-time operating system use

- Real time deterministic interrupt response

- Adds fast, low overhead hardware based security extensions with ARM TrustZone for ARMv8-M

- Enhances debug and trace with more flexible breakpoints and watchpoints

- Improves productivity by making it easier to scale solutions from the smallest to the most performant

- Makes it easier to protect code with a simpler to program memory protection unit.

There will be two variants with ARMv8-M Baseline and ARMv8-M Mainline, with the latter adding optional DSP and FPU, more instructions, etc…

Charbax is at the conference and did a good job at filming Mike Muller, ARM CTO, keynote, where he unveiled both Cortex A35 and ARMv8-M, beside addressing imprinted circuits, ARM servers (arm.com is now running on those), weak security for IoT applications, CryptoCell 700 series for Cortex A processors, Cryptocell 300 series for ARMv8-M, and mbed OS 3.0. He concludes with the new industry equation: (trust x perf)/(energy x $) to emphasize the importance of security.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

I think the naming is rather unfortunate as it’s easy to confuse A35 to A53. It’s something you seem to have done while writing this article at least 2 times I think.

@Marius Cirsta

It must have been four times…

Wait until Rockchip releases their SoC… Maybe they’ll go with RK3386 with four Cortex A35…

At least the number of cores is limited to four, so it we see an octa core Cortex A35 shown somewhere, we’ll know something is not quite right….Since Cortex A7 offered about 83% the performance of a Cortex A9, add 15% to that and you get something like 96% the performance of a Cortex A9, combine this with 10% lower consumption than a Cortex A7, the fact the design is 64 bit, in-order design, consumption that is probably something like 5-10% of a Cortex A57 (while probably offering something like 50% the performance of a Cortex A57, but considering the fact this is a 8 stages pipeline design it will not scale that good) and it looks like a brilliant design.

For those who are not impressed consider that this an inorder design, it is the new very low end for the ARM environment, a core that is mostly on par with what in 2012 was considered the high end of the ARM environment (Cortex A9).

@cnxsoft From my understanding and I also read the article from anandtech there are 4 cores in a cluster, but no limit of clusters per SOC is mentioned, so I don’t see how there is a limit to how many cores can be used in an implementation, as long as you use a multiple of 4.

@RAF

You’re right… The features are quite clear actually: “Multicore 1-4x SMP within a single processor cluster, and multiple coherent SMP processor clusters”.