Intel’s virtual FPGA Technology Day 2020 is taking place today, and the company made two announcements before the event. First, the company introduced the new Intel eASIC N5X structured eASIC family with an Intel FPGA compatible hard processor system to design to quickly create applications across 5G, artificial intelligence, cloud, and edge workloads.

In addition, Intel also announced the Intel Open FPGA Stack (aka Intel OFS), a scalable, open-source (intel calls it “source-accessible”) hardware and software infrastructure available through git repositories design to ease the work of hardware, software, and application developers.

Intel eASIC N5X

eASIC N5X is the first structure ASIC from the company to integrate an Intel FPGA compatible Quad-core Armv8 hard processor system. The new chips will help customers bring custom solutions faster to market compared to traditional ASICs thanks to the FPGA fabric, and at a cheaper cost and with up to 50% lower core power compared to FPGA chip thanks to the hard processor system.

eASIC N5X is the first structure ASIC from the company to integrate an Intel FPGA compatible Quad-core Armv8 hard processor system. The new chips will help customers bring custom solutions faster to market compared to traditional ASICs thanks to the FPGA fabric, and at a cheaper cost and with up to 50% lower core power compared to FPGA chip thanks to the hard processor system.

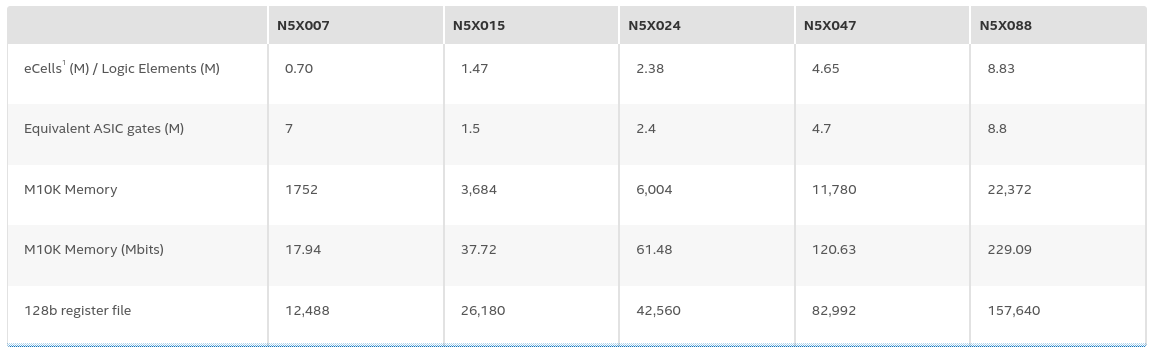

Intel eASIC N5X highlights:

- Hard processor system – Quad-core Armv8

- Up to 8.8 million equivalent ASIC gates

- Up to 229Mb of true dual-port memory and 20 Mb of 128b register files

- Up to 80x 32.44 Gbps high-speed transceivers

- Secure device manager for bring-up, security, and anti-tamper features

- 16nm process

There are currently five eASIC N5X SKUs: M5X007, M5X015, M5X024, M5X047, and M5X088 as listed below.

Intel eASIC N5X looks to share many similar features as the Intel (Altera) Agilex SoC FPGA family announced last year with a quad-core Cortex-A53 processor and FPGA fabric, and Intel did adapt the secure device manager adapted from the Intel Agilex FPGA family to integrate it into Intel eASIC N5X devices to support secure boot, authentication, and anti-tamper features.

More details may be found on the product page and announcement.

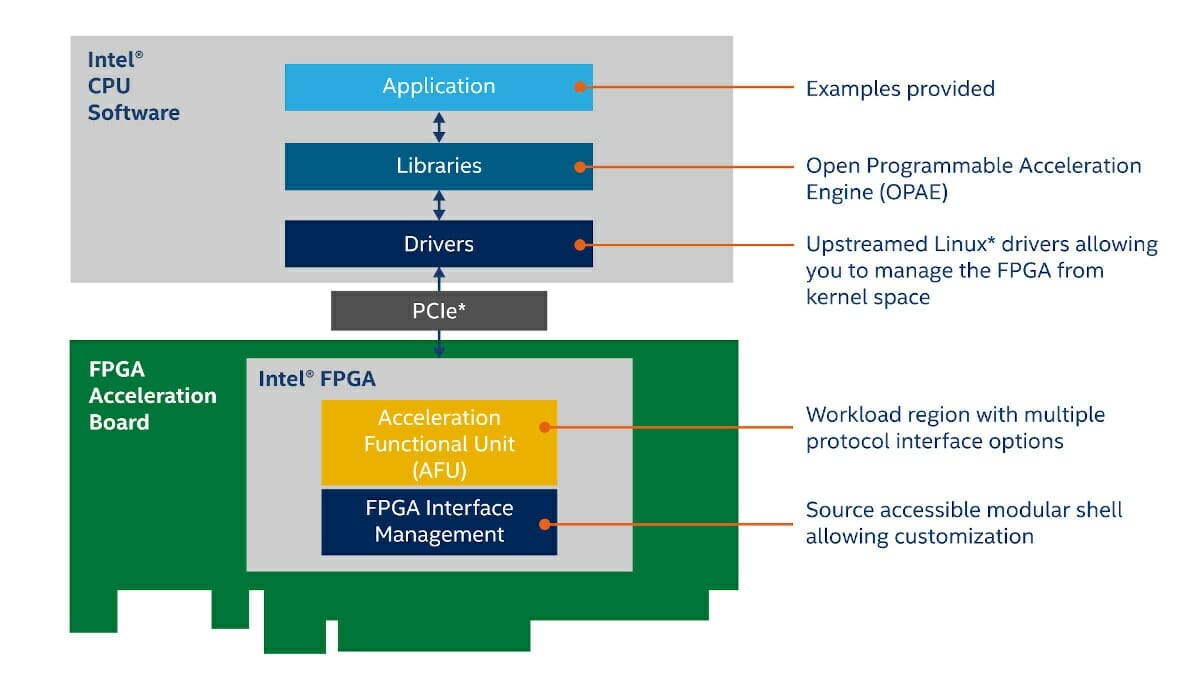

Intel Open FPGA Stack

In a separate announcement, the company also unveiled the Intel Open FPGA stack (OFS) to ease development with Linux drivers to manage the FPGA from kernel space, an Open Programmable Acceleration Engine (OPAE), and application examples running on the host, as well as resources for hardware development includes a source-accessible modular shell for FPGA interface management, and various protocol interfaces to access accelerators. The stack works on Intel Stratix 10 FPGA, Intel Agilex FPGA, and future Intel FPGA device families.

The Intel OFS is not available to all developers just yet, and if you’d like to try it out for your next project or would like more details, you’d need to access it on the Early Access Program (EAP) by contacting an Intel sales representative to get started. The EAP for Intel OFS will run for most of next year. See the announcement and product page for a few more details.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress. We also use affiliate links in articles to earn commissions if you make a purchase after clicking on those links.

How is it different from regular FPGA SoCs?

I think the ASIC part of the chip can only be programmed once, but FPGA are re-programmable.

The routing of the LUTs is fix with design input at fabrication, the LUTs are still programmable on Power application and loading, for the eASIC portion.