MIPS is dead, right? Well, there’s now very little done on the architecture itself, MIPS (the company) has decided to switch to RISC-V architecture, and unveiled the eVocore product lineup currently comprised of the eVocore P8700 and I8500 multiprocessor IP cores.

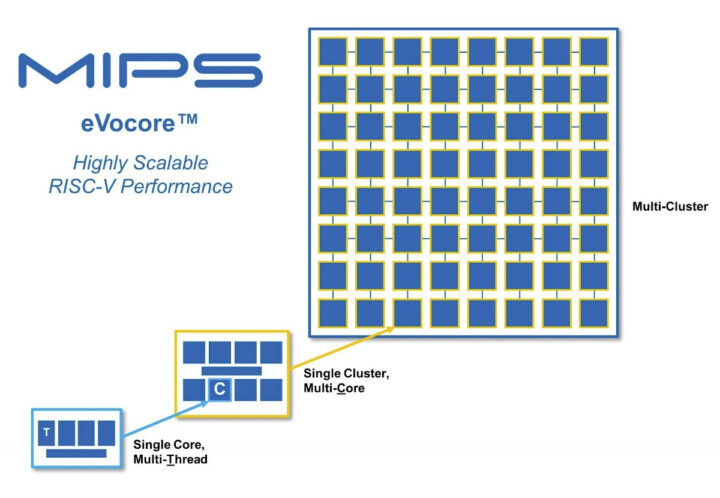

The 64-bit cores are scalable from single-core multi-thread to a single cluster with multiple cores, and up to a multi-cluster, and target high-performance, real-time compute applications such as networking, data centers, and automotive.

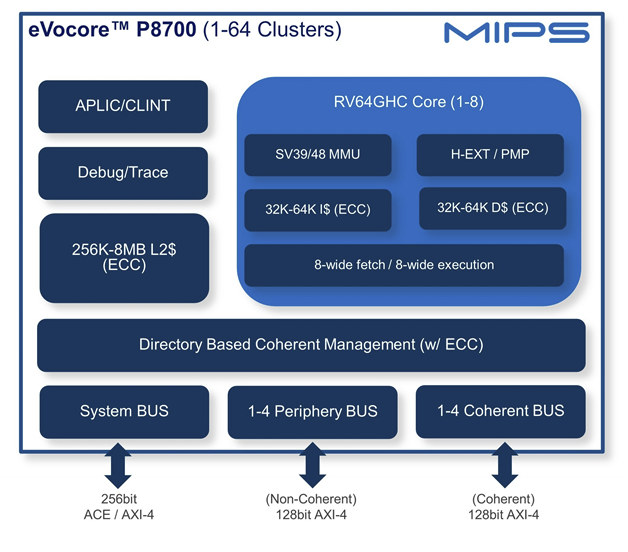

The eVocore P8700 comes with a 16-stage deep pipeline with multi-issue Out-of-Order (OOO) execution and multi-threading. MIPS claims it has single-threaded performance greater than what is currently available in other RISC-V CPU IP offerings, but did not provide any numbers. It will likely be used in the cloud and high-end servers as it can scale up to 64 clusters, 512 cores and 1,024 harts/threads.

P8700 highlights:

- Multi-issue superscalar Out of Order (OOO) with Multi-threading

- 16-stage pipeline for higher clock frequency

- 8-wide instruction fetch

- 8-execution pipes: 2xALU, MDU, 2xFPU, 2xMemory

- Enhanced Coherence Manager with L2 cache

- HW pre-fetch, widened busses, reduced latency

- 48-bit physical addressing

- 256 Interrupt support, APLIC/CLINT

- System interface

- ACE or AXI: 256-bit system bus

- Optional: Coherent Bus (up to 8 ports)

- Optional: Non-coherent periphery bus (up to 4 ports)

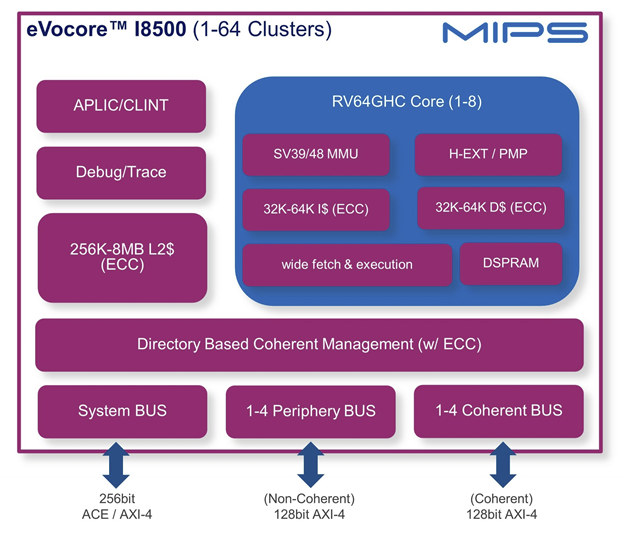

The MIPS eVocore I8500 RISC-V core aims to achieve “best-in-class performance efficiency” with an in-order multiprocessing system for use in SoC applications. Each I8500 core combines multi-threading and an efficient triple-issue pipeline.

I8500 highlights:

- In-Order with Simultaneous Multi-threading (SMT)

- 9-stage pipeline for efficient execution

- Wide instruction fetch

- 7-execution pipes: ALU, MDU, 2xFPU, 2xMemory

- Enhanced Coherence Manager with L2 cache

- HW pre-fetch, widened busses, reduced latency

- 48-bit physical addressing

- 256 Interrupt support, APLIC/CLINT

- System interface

- ACE or AXI: 256-bit system bus

- Optional: Coherent Bus (up to 8 ports)

- Optional: Non-coherent periphery bus (up to 4 ports)

MIPS apparently plans to use RISC-V user-defined instructions (UDIs) to add extra features/accelerators, while staying fully compatible with off-the-shelf RISC-V development tools and software libraries. Other features for the eVocore IP cores include privileged hardware virtualization, multi-threading, hybrid debug, and functional safety. The company expects those to be used in automotive (ADAS, AV, IVI), 5G and wireless networking, data center and storage, and high-performance embedded applications.

The eVocore P8700 will be available in Q4 2022, but no ETA was provided for the eVocore I8500 IP. A few more details may be found on the product page.

Via the RISC-V blog

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress. We also use affiliate links in articles to earn commissions if you make a purchase after clicking on those links.

I don’t want to sound negative, but “single-threaded performance greater than what is currently available in other RISC-V CPU IP offerings” isn’t particularly attractive considering what has been shown to date. I don’t think that RISC-V solutions should compete against each other, it’s not as if there was already a large RISC-V demand. They’d rather first try to convince users to switch from x86/ARM to RISC-V and provide performance comparisons against available 2020-era cores and not cores that still seem to have been designed for education purposes and cheap MCU designs.

What’s really impressive in their design here is the horizontal scalability. But stuffing that many cores (and threads) into a single CPU still requires very specific workloads. That’s how GPUs work for example, and they’re not for every day applications. Possibly that the chip can be used for massive low-cost VM hosting. But this needs to come with massive memory bandwidth. And hosting that many users on single machines on OOO designs reminds that there are always Spectre-like threads lurking around.

It’s not clear that they actually changed the design much from what they advertised back in 2016, see https://www.cnx-software.com/2016/10/13/imagination-technologies-announces-mips-warrior-i-class-i6500-heterogeneous-cpu-with-up-to-384-cores/

The I8500 design is probably very close to the i6500, other than the ISA. The 9-stage, dual-issue pipeline is similar to a Cortex-A53 in principle, but I have never seen any actual benchmark numbers. The P8700 is likely derived from the P6600, which in turn is comparable to early Cortex-A7x cores.

In earlier marketing materials (see https://zhuanlan.zhihu.com/p/288052811), they had mentioned I8800 and I8100 cores, but not the P8700.

Shouldn’t the article or the specs tell which RISC-V implementation it is? Which Extension, in which Version.

See https://www.cnx-software.com/2019/08/27/risc-v-bases-and-extensions-explained/

Oh, wait, the diagram says “RV64GHC”, so let’s check:

Still no version spec, though. Pity.

FWIW: I have a D1 RISC-V, which Linux identifies as “rv64imafdcvu”, meaning:

RV64I Base Integer Instruction Set, 64-bit

plus mafdcvu meaning:

Alas, the D1 has one Extension only in version 0.6 (instead of 1.0), causing problems (read: program crashes) with FENCE.TSO

The MIPS eVocore P8700 RISC-V core is now available.

https://www.mips.com/news/mips-announces-availability-of-its-first-risc-v-ip-core-the-evocore-p8700-multiprocessor