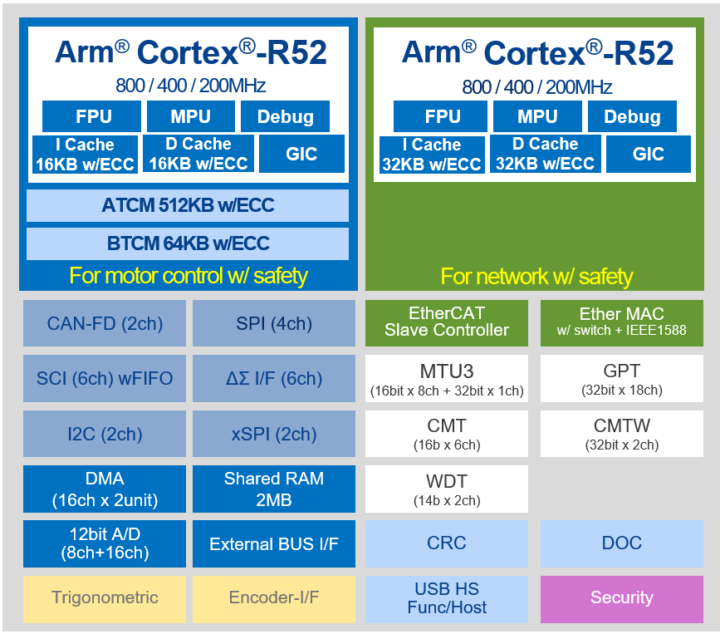

Built around two Arm Cortex-R52 cores clocked at up to 800 MHz, Renesas RZ/T2M microprocessor units (MPUs) target real-time, high-precision motor control applications such as AC servo drives and industrial robots.

The RZ/T2M microprocessor also supports Ethernet with TSN and functional safety, and has been designed in such a way to reduce the number of external components in order to both decrease the BoM costs and the product size.

Renesas RZ/T2M key features and specifications:

- CPU – Up to 2x Arm Cortex-R52 cores clocked at up to 800MHz, one core for motor control, and the other for networking

- Trigonometric function accelerator

- Memory – Tightly coupled memory 576KB with ECC, 2MB RAM with ECC

- Storage I/F – Octa/Quad SPI support

- Networking

- 3-port Gigabit Ethernet switch with TSN

- Industrial Ethernet: EtherCAT, PROFINET RT/IRT, EtherNet/IP, etc…

- Motor control

- 2-channel encoder interface with support for A-format, EnDat, BiSS, HIPERFACE DSL, Tamagawa

- Functional safety support up to SIL3

- Motor current loop < 1µs

- 3-phase complementary PWM output for dual motor control

- 6-channel ΔΣ I/F

- Other I/Os

- 2x 12-bit ADC

- USB – 1x USB 2.0 high-speed host/functions

- 2x CAN FD (compliant with ISO11898-1)

- 6x SCI with 16-byte transmission and reception FIFOs

- 3x I2C, 4x SPI, 2x xSPI

- Voltages – Core 1.1V, I/O 3.3/1.8V

- Packages – 320-pin BGA, 225-pin BGA, 176-pin QFP, 128-pin QFP

- Temperature Range – -40 to +125°C

The Renesas RZ/T2M microprocessor can be programmed with the Eclipse-based e² studio IDE or IAR Embedded Workbench for Arm, and a “Flexible Software Package” (FSP) is also provided.

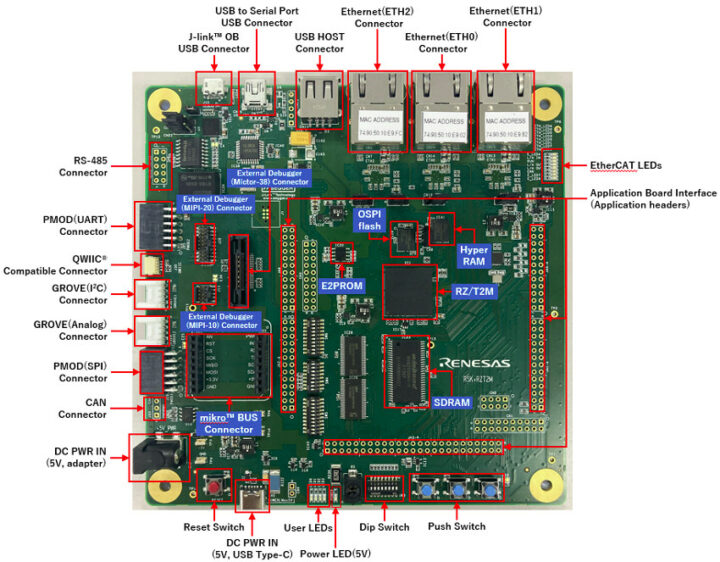

The company can also provide the Renesas Starter Kit+ for RZ/T2M (RZ/T2M-RSK) evaluation and development kit with the following highlights:

- MPU – Renesas RZ/T2M MPU, 320-pin package (R9A07G075M24GBG)

- System Memory – 256 Mbit SDRAM, 64 Mbit HyperRAM

- Storage – 256 Mbit NOR Flash, 512Mbit Octa Flash, 5Mbit QSPI flash, 16Kbit I2C EEPROM

- Networking – 3x Gigabit Ethernet port

- USB – 1x USB Host port

- Serial – RS485, CAN connector

- Expansion – Pmod, Groven QWIIC, mikroBUS

- Debugging – On-board emulator circuit (J-Link), USB to TTL connector

- Power Supply – 5V via DC jack

The kit also includes all necessary cables to get started.

The Renesas TZ/T2M MPUs and evaluation kit are available now with the latter going for about $440 US. More details, including extensive documentation and purchase links, can be found on the product page.

Thanks to TLS for the tip.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

I’m always puzzled when seeing high-frequency real-time processors like this, with 2 levels of cache and with high performance I/O (e.g. 3*GigE). It’s probably not be easy to sustain the 1us accuracy, and that makes me wonder how long the distinction between real-time and application will be able to stand. I suspect that development rules will progressively include a wide number of constraints (such as low-lat unless network is flooded with broadcasts, etc), and that such constraints might end up also being efficient for application processors, and possibly sufficient most of the time. But maybe I’m totally wrong.

For the motor control CPU, it’s actually one level of cache: 16K each for instructions and data. The 576K of TCM (tightly coupled memory) is not a cache; you would put your real time code in there. The 2MB shared memory is also not cache.

If you look at the roughly compared TI part (AM62x), you’ll see it has an optional real time Cortex-M4 processor. NXP, ST, and IIRC Renesas, also have chips with the same main CPU / real time CPU setup.

Good points indeed. Then I agree that TCM can help make a huge difference with more common architectures.

Estoy comenzando con la conversión de una milling manual a cnc.