Allwinner is mostly known for its low-cost Arm processor running Android or Linux, but the Allwinner R128 is a wireless audio SoC with a C906 64-bit RISC-V application core, an Arm Cortex-M33 real-time time core, a HiFi 5 DSP, and built-in WiFi and Bluetooth connectivity.

The SoC also comes with 1MB SRAM, up to 16MB flash, up to 32MB PSRAM, display and camera interfaces, support for microphone arrays, and plenty of I/Os that should make it suitable for smart speakers and other voice-controlled home appliances with or without display.

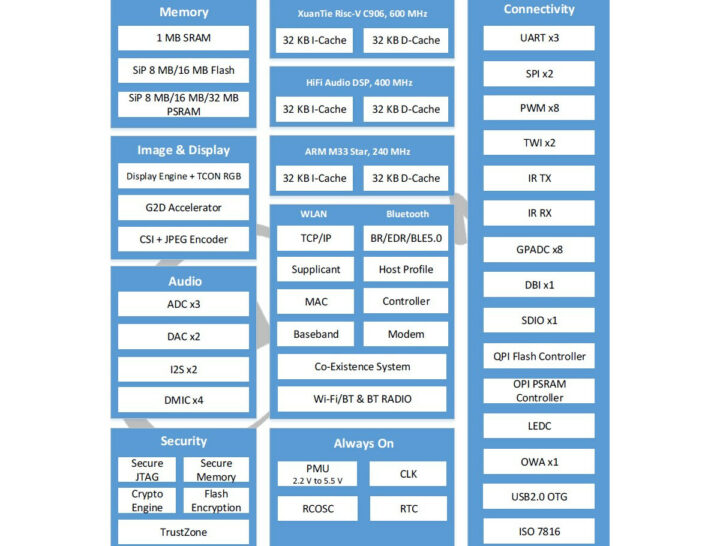

Allwinner R128 specifications:

- Application core – Xuantie C906 64-bit RISC-V core clocked at 600 MHz.

- DSP – Cadence HiFi 5 audio DSP clocked at 400 MHz

- Communication core – Arm M33 Star (Cortex-M33 from Arm China?) core clocked at 240 MHz with Trustzone support

- Memory

- 1MB SRAM

- 8MB, 16MB, or 32MB PSRAM (SiP = System-in-Package)

- OPI PSRAM controller

- Storage

- QPI flash controller

- 8MB or 16MB flash (SiP)

- Display – TCON (RGB666) and SPI-DBI LCD interfaces up to 104×768 @ 60 fps with 2D graphic accelerator

- Camera – DVP interface with JPEG encoder @ 720p24

- Audio

- 3x ADC, 2x DAC

- 4x DMIC

- 2x I2S

- Wireless

- 2.4 GHz 802.11b/g/n WiFi 4 with WPA3 security

- Dual-mode Bluetooth 5.0 BR/DR and Low Energy (LE) with support for Long Range and Bluetooth Mesh

- Peripherals

- 3x UART, 2x SPI, 8x PWM, 2x I2C/TWI

- IR Tx and Rx

- 8x general-purpose ADC

- USB 2.0 OTG

- ISO/IEC 7816 smart card support

- Supply Voltage – 2.5 to 5.5V Vbat single power supply

That’s about all the public information we have so far (from Twitter), as Allwinner R128 is not listed on the company’s website just yet. But we can do some informed speculation. The 64-bit RISC-V core is the same core as on the 1GHz Allwinner D1 SoC, except clocked at 600 MHz only, but it may run FreeRTOS or another RTOS like RT-Thread instead, as Linux may not be too happy even on a SiP with 32MB SPRAM because this type of memory is usually slow. It’s not to say it’s impossible, after all, ESP32 can run Linux too, but Linux will not be the primary OS on the Allwinner R128 SoC.

The Arm Cortex-M33 core should handle the WiFi and Bluetooth connectivity and the firmware should probably be closed-source because it handles the wireless part. The HiFi 5 audio DSP is designed for voice-controlled appliances and takes care of audio pre-processing and speech recognition/keyword detection. I can also see references to “Vbat” so I suspect it will be used on battery-operated devices as well.

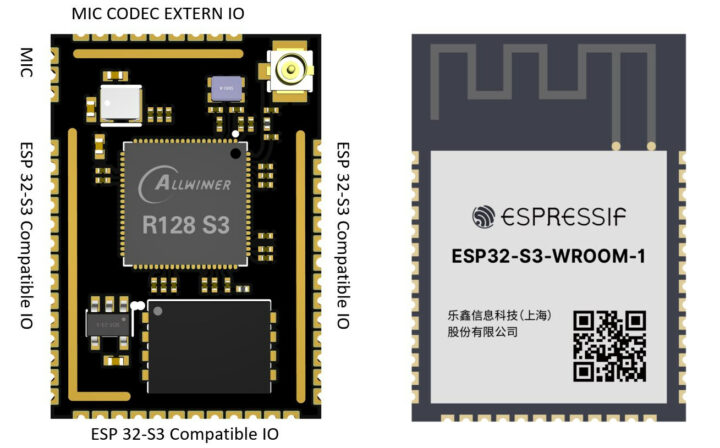

It looks like an alternative to some Espressif Systems and Bouffalo Labs wireless SoCs designed for applications that may benefit from a more powerful application processor, as well as some extra features such as a JPEG encoder and a 2D graphics accelerator. We’ll have to wait to find out… [Update: GLGH_ has shared a render of an Allwinner R128 S3 module with the same pinout as the ESP32-S3-WRROM-1 module, except for additional castellated holes for audio

]

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress. We also use affiliate links in articles to earn commissions if you make a purchase after clicking on those links.

If only it had 64MB of memory.

Talk about a wierd Franken-chip. ARM, RISC-V (T-head no less), and some Cadence stuff? Of the three, maybe one of those will actually be licensed–and that’s only because it’s available under an open license. Good luck importing these chips or the devices made from them anywhere.

Agreed, it has already happened with R329, basically unobtainable mcguffin in “the West”.

This is really a frankenstein of a chip. I am unsure why you need a HiFi 5 for such a small embedded system, many modern-ish desktop systems have HiFi 3(which is less wider) at similar clocks.

As an example, from the OSF project

With Bay Trail having a HiFi 2. that goes from 50-400 MHz, which is also the same that platforms like Broadwell had.

It’s really overkill and I am really not sure why. Those days, Intel/AMD SoCs put some more ooomph on their audio system just to put more AI stuff into it(like say an Audio Denoiser), that doesn’t appropriate here.

Then you add in the ARM and RISC-V core, the slow PSRAM and etc.

In the block diagram it also has a block that says ‘TCP/IP’, would it mean that it has some packet offloading/acceleration? Doesn’t say anything of the sorts in the specs.

Probably for audio recognition, so this can be used in a product like an Alexa and get the user audio input.

That could have been handled in the RISC-V core is supposed to have a very nice(for an embedded system) Vector Unit that can do either INT to FP operations(including INT8/INT16/INT32/INT64/FP16/FP32).

It just seems way overkill to put a Tensilica HiFi 5 there. Plus it will probably be terrible bottlenecked by the memory bus as it doesn’t have TCM, only caches.

The SRAM should be reasonably fast but it’s not large enough for a lot of voice processing/neural networks stuff.

The T-head RISC-V core has a pre-standard vector extension, so unless you’re getting a library from T-head, don’t count on using that extension. You have to use a T-head mangled GCC to even generate code for it.

Plan on doing your work on the DSP.

Leave it to gloomy ghost to show us the impending pinout compatibility fun…